## Contents

| AN0034 – Syfer Capacitor Basics                                          | 3   |

|--------------------------------------------------------------------------|-----|

| AN0001 – FlexiCap™ Termination                                           | 10  |

| AN0002 – Bend Testing - Methods and International Specifications         | 21  |

| AN0004 – Quality & Reliability Data                                      | 29  |

| AN0005 – Mechanical Cracking                                             | 36  |

| AN0006 – Capacitance Ageing of Ceramic Capacitors                        | 43  |

| AN0007 – Stack Chip Components - Handling and Usage                      | 51  |

| AN0008 – Restricted Substances and Lead Free Soldering                   | 55  |

| AN0009 – AEC-Q200 Stress Test Qualification                              | 66  |

| AN0010 – The Effect of Lead Free soldering on Bend Test Performance      | 73  |

| AN0011 – Solder Alloy Choice                                             | 81  |

| AN0012 – Electronic Lighting Ballasts                                    | 107 |

| AN0013 – Packaging Labels (RoHS and Pb Free Compliance Labelling)        | 112 |

| AN0014 – X2Y Balanced Line EMI Chip (Reliability and Performance Data)   | 115 |

| AN0016 – Micro sectioning of Multilayer Ceramic Capacitors               | 125 |

| AN0018 – EMI Suppression of DC Motors using X2Y                          | 132 |

| AN0019 – Tin Whiskers - Syfer Surface Mount Capacitors                   | 135 |

| AN0021 – Tandem Capacitors                                               | 143 |

| AN0022 – Open Mode Capacitors                                            | 149 |

| AN0024 – IPC/JEDEC J STD 020D Moisture/Reflow Sensitivity Classification | 155 |

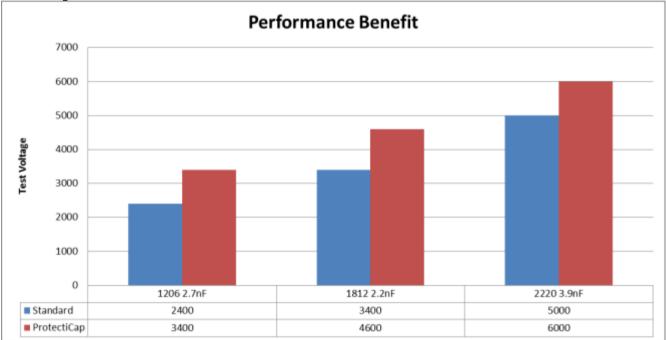

| AN0025 – LCD Inverter Range – 5kV and 6kV Surface Mount Capacitors       | 163 |

| AN0026 – ECSS-Q-70-02A - Thermal Vacuum Outgassing Test                  | 166 |

| AN0027 – European REACH Regulation                                       | 182 |

| AN0028 – Soldering/Mounting Chip & Radial Capacitors and EMI Filters     | 186 |

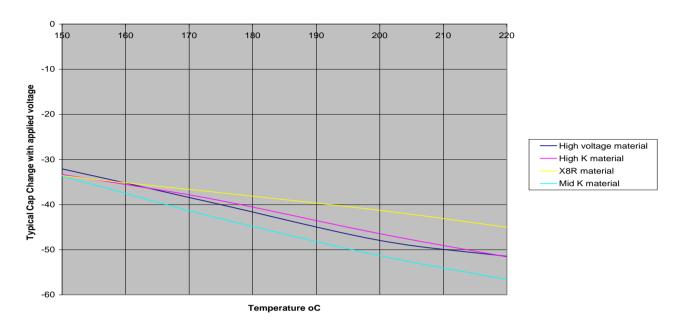

| AN0029 – Use of Syfer MLCCs at Higher Temperatures                       | 194 |

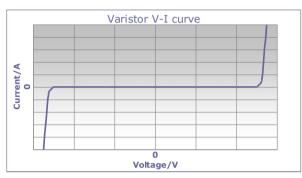

| AN0031 – Metal Oxide Varistor Planar Arrays                              | 201 |

| AN0032 – MLCCs for use in Modems                                         | 208 |

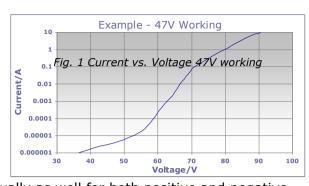

| AN0033 – AC250 Range: Non-Safety AC MLCC for use at Mains Voltages       | 211 |

| AN0035 – Magnetic Characteristics of Syfer Products                      | 215 |

| AN0036 – High Q MS Capacitor Range                                       | 219 |

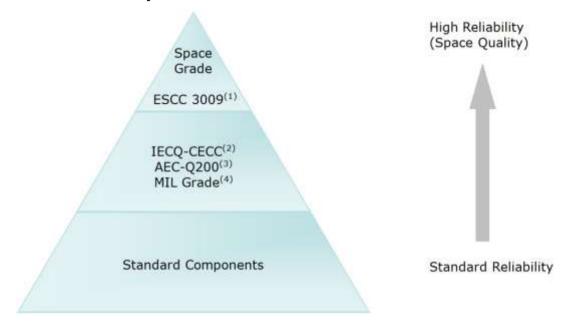

| AN0037 – IECQ-CECC Range                                                 | 228 |

| AN0038 – ProtectiCap™                                                    | 234 |

| AN0039 – StackiCap™                                                      | 240 |

| AN0040 – Residual Capacitance Range VC1                                  | 247 |

| ANO042 - PSI Range with FleviCan™ Termination                            | 252 |

Knowles (UK) Limited, Old Stoke Road, Arminghall, Norwich, Norfolk, NR14 8SQ, United Kingdom Tel: +44 (0) 1603 723300

Tel. (Sales): 01603 723310

Fax: +44 (0) 1603 723301

Email: SyferSales@knowles.com

Web: www.knowlescapacitors.com/syfer

## Syfer Capacitor Basics

| What is a Capacitor                       | . 2 |

|-------------------------------------------|-----|

| Electrode                                 | .2  |

| Dielectric                                | .2  |

| Construction                              | .2  |

| MLCC Uses                                 | .3  |

| Limitations and Factors for Consideration | .3  |

| Dielectric Types                          | .4  |

| X7R                                       | .4  |

| X5R                                       |     |

| X8R                                       | .5  |

| 2C1 (BZ) and 2X1 (BX)                     | .5  |

| COG                                       |     |

| High Q                                    | .5  |

| Useful Formulae and Calculations          | .6  |

| Recognising a Syfer Part Number           | .6  |

Page 2 of 7

#### What is a Capacitor

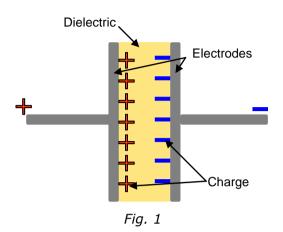

A capacitor is a charge storing device consisting of two or more conducting plates separated from one another by an insulator. These two constituent parts are called the electrode and the dielectric.

#### Electrode

The electrode must be a good conductor of electricity, materials widely used in capacitor manufacture are:

Aluminium

Copper

Nickel

Palladium

**Platinum**

Silver

**Tantalum**

Depending on the manufacturing process used the electrode may also be required to be unreactive and have a high melting point. This is the case for oxidising atmosphere fired ceramic capacitors which are manufactured at Syfer. The sintering temperature of the ceramic dielectric material is around 1100°C; in order to stop the electrode from melting during firing a combination of Silver and Palladium is used. This method of manufacture is referred to as the PME or Precious Metal Electrode system.

#### Dielectric

The dielectric must be a good insulator, materials widely used in capacitor manufacture are:

Ceramic  $\varepsilon_r$  15-10000

Porcelain  $\epsilon_r$  6

Metal Oxide  $\epsilon_r$  12

Mica  $\epsilon_r$  5.4

Plastic Film  $\epsilon_r$  3

Dielectrics have other important characteristics other than their ability to insulate. Dielectric constant or relative permittivity,  $\epsilon_r$ , is one of the most important. This is the dominant characteristic in determining the capacitance value attainable at a given size and voltage, the value relates to the permittivity of a vacuum which has a  $\epsilon_r$  of 1. The ceramics used by Syfer are split into two main types, COG/NPO which have  $\epsilon_r$  values of between 20 and 100 and X7R which have  $\epsilon_r$  values of between 2000 and 3000.

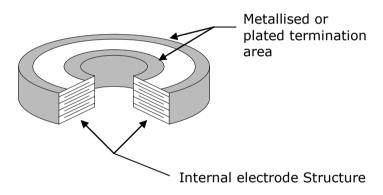

#### **Construction**

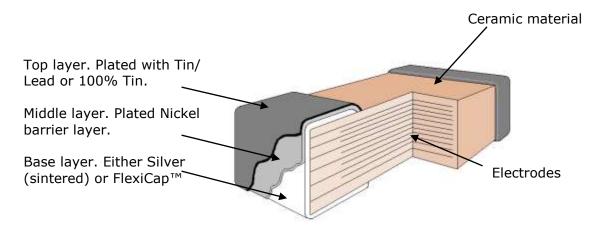

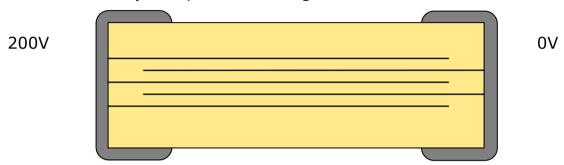

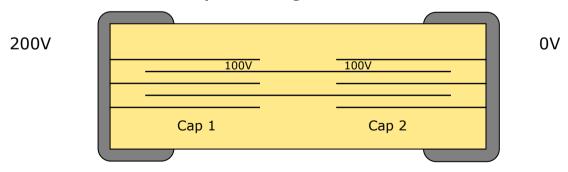

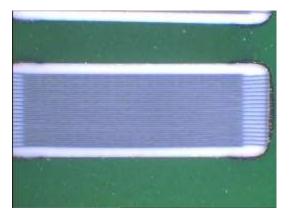

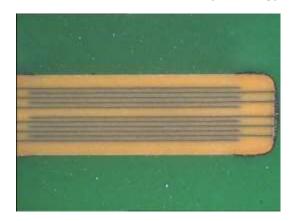

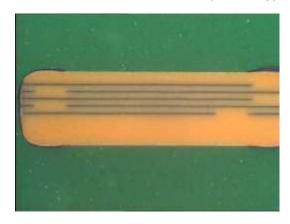

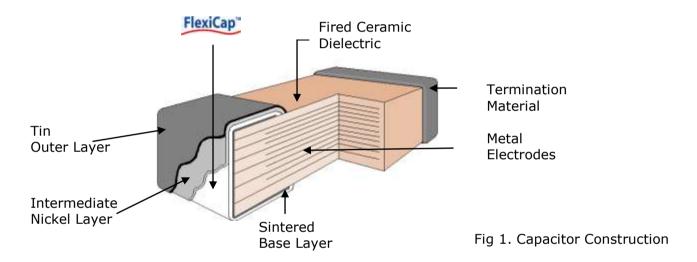

The most basic type of capacitor is a single layer which is shown in Fig. 1 and consists of a layer of dielectric material sandwiched between a positive and a negative electrode. The MLC capacitor, which Syfer produce, takes this concept and multiplies the number of layers to increase the available capacitance hence multilayer ceramic capacitor, see

Fig.2. Layers of ceramic are built up using a screen printing process, these are interleaved with electrodes of alternating polarity. The like polarity electrodes are then joined together using a

Page 3 of 7

termination material. The termination can then be attached to wires or legs to form a radial leaded MLCC or electroplated to form a surface mount MLCC.

#### **MLCC Uses**

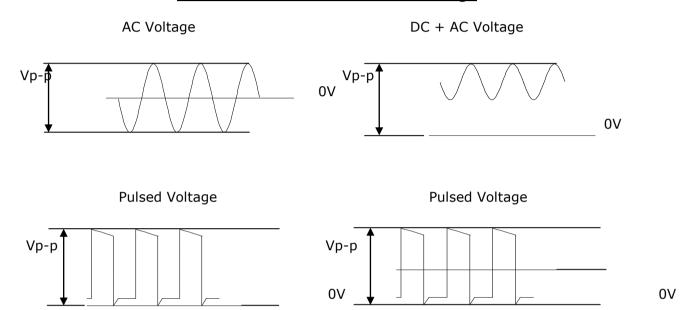

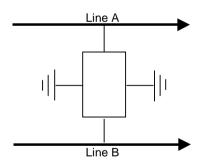

A MLCC has many different applications in electronic circuits. However, the three main uses are: *Blocking*:

A capacitor has dc voltage applied combined with a much smaller ac signal voltage. An important application of capacitors is to stop direct current (dc) but allow alternating current (ac) from one part of an electronic circuit to another. A dc voltage is blocked when the capacitor is charged but if a varying (alternating positive and negative) voltage is applied then a current will flow first in one direction, then in the other as the capacitor charges and discharges. You will find capacitors used in this way in T.V. Radio and Audio Amplifiers.

#### Frequency Selection:

Capacitors are used to help detect Radio Frequency and they are part of the tuning circuit. Again, they are used in T.V. and Radio circuits.

They can also be used to 'filter out' frequencies, which could interfere with the equipment.

#### Storage of Electrical Energy/Smoothing:

The ability of capacitors to store charge is used to stabilise the voltage to sensitive devices. This application accounts for a large proportion of all MLCCs used. The capacitors are utilised close to the memory chips in computers and ensures that the chip operating voltage stays constant in spite of the electrical activity going on all around. The same property is used to smooth the outputs from power supplies and voltage converters.

#### **Limitations and Factors for Consideration**

Capacitance (C) is:

Directly proportional to electrode overlap area (A)  $C \alpha A$

Directly proportional to dielectric constant  $(\varepsilon_r)$   $C \alpha \varepsilon_r$

Inversely proportional to dielectric layer thickness (*T*)  $C \alpha \frac{1}{T}$

Voltage rating is related to a non linear positive function of dielectric thickness.  $V_w = f.T$

These relationships have knock-on effects on the amount of capacitance available at set sizes and voltages. Smaller footprint and restricted thickness limit the available capacitance value. Higher voltage capacitors need greater dielectric thickness which means less capacitance, this is not a linear function, especially for high voltage capacitors. For example, to increase the voltage from 1000V to 2000V requires a typical doubling of dielectric thickness; this in turn means that only half the number of electrodes can fit into a set thickness. Due to the fact that capacitance is directly proportional to overlap area and inversely proportional to dielectric thickness; the overall capacitance available in a given size at 2000V is roughly 25% of that at 1000V.

Page 4 of 7

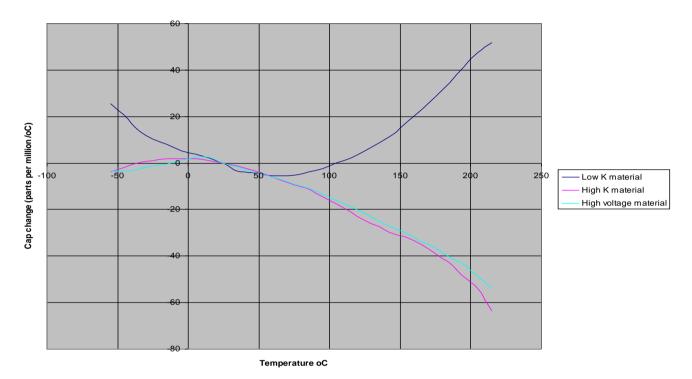

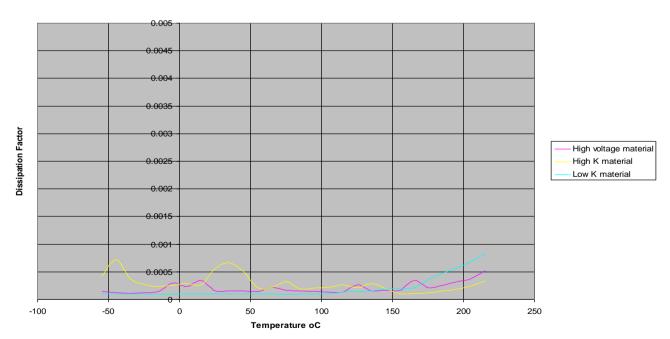

#### **Dielectric Types**

There are many types of dielectric material each of which have their own characteristics and therefore uses. Syfer use predominantly Barium Titanate and Neodymium Titanate based dielectric materials which, in different formulations and designs make X5R, X7R, X8R, 2C1(BZ) and 2X1(BX) and C0G materials, Syfer also have a High Q material. There is a trade off between  $\epsilon_r$  and stability and loss. Generally speaking dielectrics with a higher  $\epsilon_r$  value, are less stable with temperature, time and voltage than those with a lower  $\epsilon_r$  value. The main stability characteristics are defined as:

$T_{CC}$  – Temperature Coefficient of Capacitance, how much capacitance changes with temperature

$V_{CC}$  – Voltage Coefficient of Capacitance, how much capacitance changes with applied voltage

Ageing – How much capacitance changes over time

${\it DF}$  and  ${\it Q}$  – Dissipation Factor and Quality factor, reciprocals of each other and measure the losses with the capacitor

The different material codes help define the performance of the dielectric material

|   | I                      | EIA C | Class 2 Classification | 1   |                               |

|---|------------------------|-------|------------------------|-----|-------------------------------|

|   | Minimum<br>Temperature |       | Maximum<br>Temperature | Сар | pacitance Change<br>Permitted |

| X | -55°C                  | 4     | +65°C                  | Α   | ±1.0%                         |

| Υ | -30°C                  | 5     | +85°C                  | В   | ±1.5%                         |

| Z | -10°C                  | 6     | +105°C                 | С   | ±2.2%                         |

|   |                        | 7     | +125°C                 | D   | ±3.3%                         |

|   |                        | 8     | +150°C                 | Е   | ±4.7%                         |

|   |                        | 9     | +200°C                 | F   | ±7.5%                         |

|   |                        |       |                        | Р   | ±10%                          |

|   |                        |       |                        | R   | ±15%                          |

|   |                        |       |                        | S   | ±22%                          |

|   |                        |       |                        | Т   | +22% / -33%                   |

|   |                        |       |                        | U   | +22% / -56%                   |

|   |                        |       |                        | V   | +22% / -82%                   |

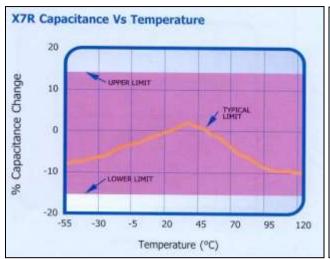

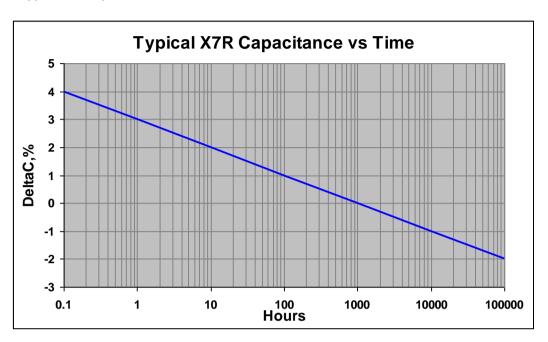

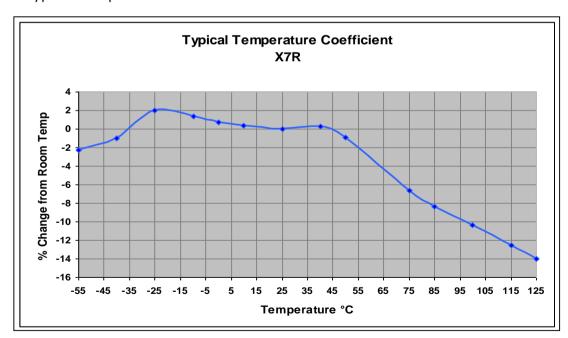

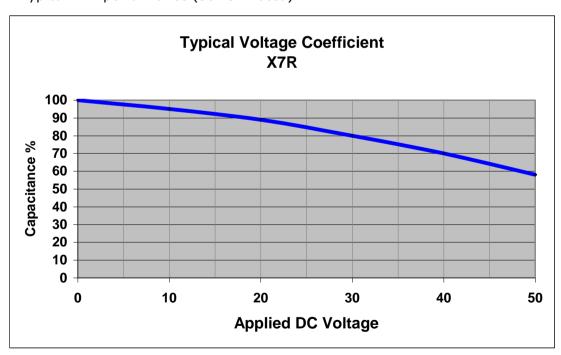

#### X7R

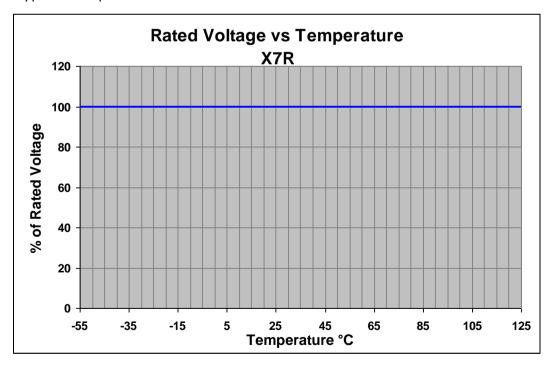

X7R is an EIA Class II dielectric; Syfer dielectric code 'X'

The 'X' and '7' define the lower and upper operational temperature range, i.e., -55°C and  $\pm 125$ °C respectively and 'R' defines the stability within the temperature range, in this case  $\pm 15$ %.

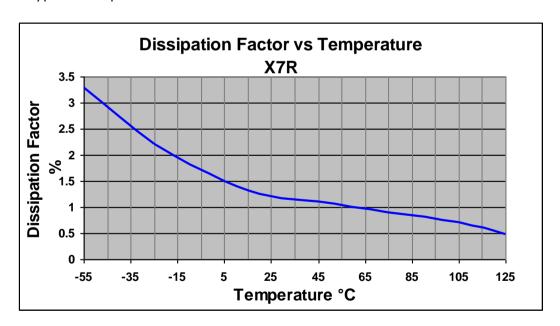

Dissipation factor is a maximum of 2.5%

$V_{\text{CC}}$  is unspecified for standard X7R material.

The ageing rate for X7R is typically 1% to 2% per time decade which means that, at 1% ageing, 2% of the capacitance value will be lost between hour 10 and hour 1000. Syfer supply X7R capacitors to their 1000 Hour capacitance value.

X7R has a high  $\varepsilon_r$  value of around 3000 and is used for capacitance values in the nF to  $\mu$ F range. X7R capacitors are generally used in energy storage, smoothing and filtering applications.

Page 5 of 7

#### X5R

X5R is an EIA class 2 dielectric Syfer dielectric code 'P'.

X5R is generally similar to X7R except that the top operational temperature limit denoted by the 5' is +85°C.

X5R capacitors are used in similar applications to X7R but where the environmental conditions are more stable.

#### X8R

X8R is an EIA class 2 dielectric Syfer dielectric code 'N'.

X8R is generally similar to X7R except that the top operational temperature limit denoted by the '8' is +150°C.

X8R capacitors are used in similar applications to X7R but where the environmental conditions require stability at higher temperatures. Automotive under hood, industrial and down hole applications are some examples.

#### 2C1 (BZ) and 2X1 (BX)

Syfer dielectric codes 'R' and 'B'.

These dielectric classifications are based on X7R dielectrics but include a  $V_{CC}$  specification and a different  $T_{CC}$  requirement.

2C1 has  $T_{CC}$  of  $\pm 20\%$  and a  $V_{CC}$  of  $\pm 20\%$ -30% with rated voltage applied.

2X1 has  $T_{CC}$  of  $\pm 15\%$  and a  $V_{CC}$  of +15%-25% with rated voltage applied.

These dielectric classifications are useful where a more defined and stable capacitance value is required.

#### COG

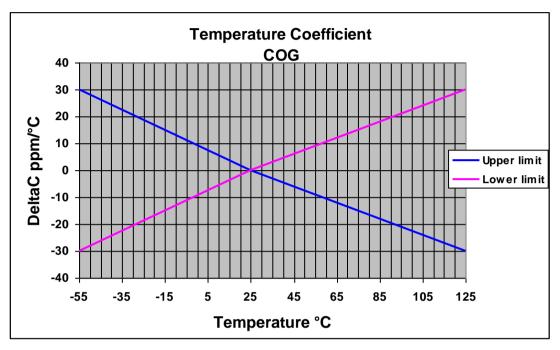

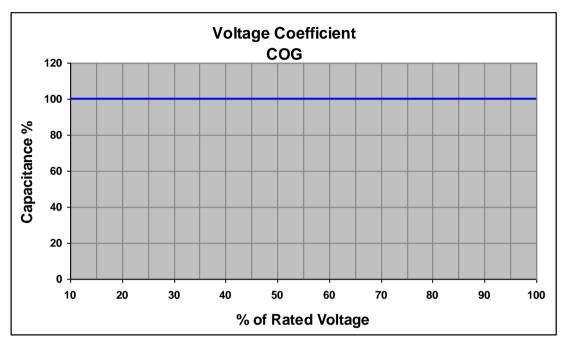

COG is an EIA Class I dielectric, it is also known as NPO, the Syfer dielectric code is 'C'. COG is much more stable than the EIA Class 2 dielectrics.

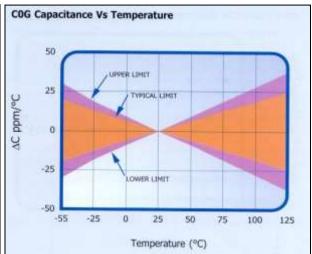

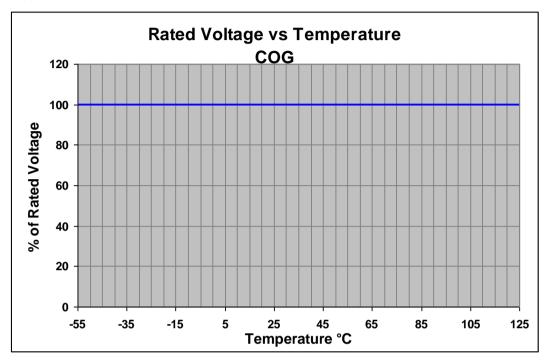

$T_{CC}$ , COG is defined as having an allowable capacitance change of  $\pm 30$ ppm/°C over the -55°C to +125°C operational temperature range.

$V_{CC}$ , COG is stable with voltage.

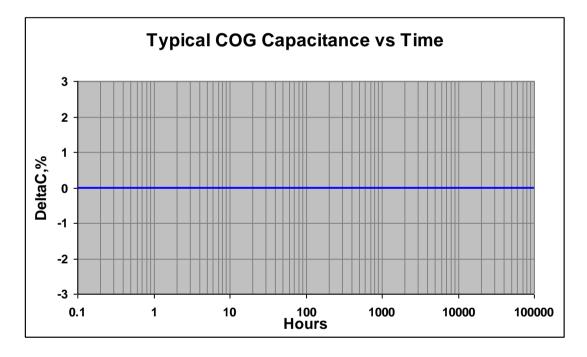

COG has negligible ageing.

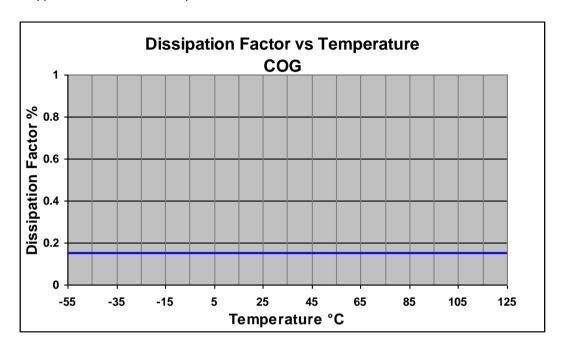

COG has a lower DF, or higher Q than X7R, defined as a maximum of 0.15%. This means that when operating at higher frequencies the power lost in the capacitor is reduced and it is less inclined to overheat.

COG dielectrics have  $\varepsilon_r$  values of between 20 to 100 and are used to make stable lower capacitance parts in the pF to nF region. These are typically used for filtering, balancing and timing circuits.

#### High Q

High Q is a COG dielectric, the Syfer dielectric code is 'Q'.

Generally similar to standard COG except that the DF is lower/ Q is higher.

High Q material has a low  $\epsilon_r$  value and is used to make parts typically in the pF range, these are used generally in high frequency applications which require low losses.

Page 6 of 7

#### **Useful Formulae and Calculations**

$Q = \frac{1}{DF}$

Q is Quality Factor, DF is Dissipation Factor

$X_c = \frac{1}{2\pi fC}$

X<sub>c</sub> is Capacitive Reactance in Ohms, f is frequency in Hertz and C is capacitance in

**Farads**

$R_s = DF.X_c$  R<sub>s</sub> is Equivalent Series Resistance in Ohms, DF is Dissipation Factor and X<sub>c</sub> is Capacitive Reactance in Ohms

$P = I^2 R$

P is Power dissipated in capacitor in Watts, I is rms current in Amps and R is  $R_{\rm s}$  in Ohms

#### **Recognising a Syfer Part Number**

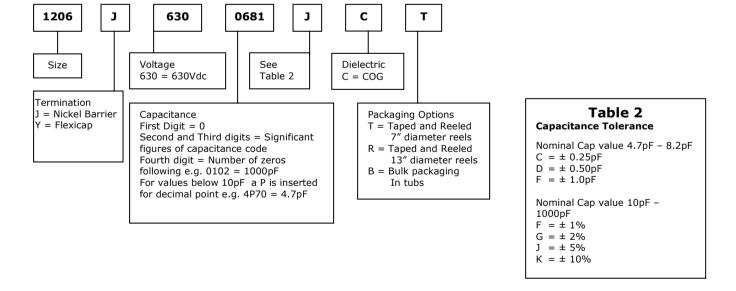

A standard Syfer part number is 15 characters long, e.g., 1206J5000682KXT. This breaks down into:

| Case Size | Termination | Voltage | Capacitance | Tolerance | Dielectric | Packaging |

|-----------|-------------|---------|-------------|-----------|------------|-----------|

| 1206      | J           | 500     | 0682        | K         | X          | Т         |

Case Size

| 1206 | J | 500 | 0682 | K | Χ | Т |  |

|------|---|-----|------|---|---|---|--|

|------|---|-----|------|---|---|---|--|

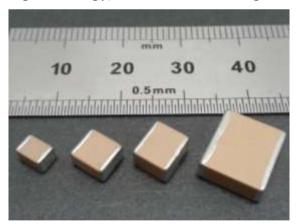

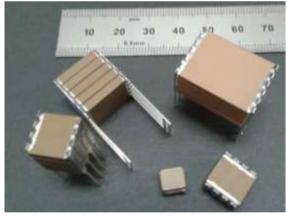

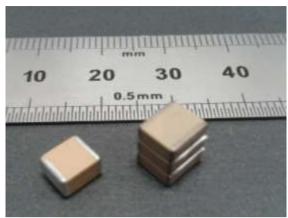

The four case size characters represent the X and Y dimensions in thousandths of an inch. Syfer's range goes from 0402 (40 thou by 20 thou) to 8060 (800 thou by 600 thou).

**Termination**

| 1206 J | 500 | 0682 | K | Χ | Т |  |

|--------|-----|------|---|---|---|--|

|--------|-----|------|---|---|---|--|

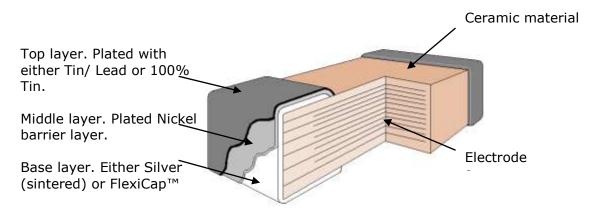

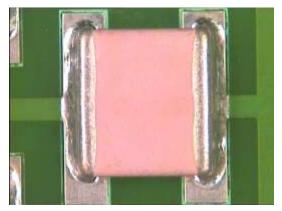

Code 'J' is the industry standard glass frit type termination. Glass material loaded with silver is applied to the ends of the capacitor. Sintered on at high temperature it ensures contact with the ends of the internal electrodes. The termination is then electroplated with Nickel and Tin.

'Y' termination, trade name FlexiCap™, is the termination material which introduced the world to flexible terminations. Pioneered by Syfer it protects the body of the capacitor from mechanical stress. Polymer material loaded with Silver is cured onto the ends of the capacitor to make an excellent bond with the internal electrodes. The termination is electroplated with Nickel and Tin.

'A' and 'H' terminations are similar to 'J' & 'Y' respectively but are electroplated with a minimum Lead content of 10%. (Used primarily in military and space applications to combat the potential problem of tin whisker growth in certain environments.)

Termination codes '2', '3', '4' and '5' are the equivalent of 'J', 'Y', 'A' and 'H' terminations but with a Copper barrier layer rather than Nickel. They provide a non-magnetic termination finish with excellent solder leach resistance.

Code 'F' is an un-plated Silver Palladium loaded glass frit termination for non-magnetic and epoxy bonding applications.

Voltage

| 1206 | J | 500 | 0682 | Κ | Χ | Т |

|------|---|-----|------|---|---|---|

010 - 999 are straightforward 10V to 999V, 1kV and above are in kV with the K as a decimal point so 1K5 is 1.5kV up to 12K for 12kV.

Page 7 of 7

Capacitance

| 1 | .206 | J | 500 | 0682 | K | Χ | Τ |

|---|------|---|-----|------|---|---|---|

|---|------|---|-----|------|---|---|---|

The first three digits are significant figures and the fourth digit is a base 10 multiplier with the final value being in picofarads (pF). For example  $0682 = 068 \times 10^2 = 6800$ pF

A 'P' or 'N' is used to specify fractions to denote the decimal point, so 4P70 would be 4.7pF and 12N4 would be 12.4nF

#### Tolerance

| 1206 J 500 0682 K X T |

|-----------------------|

|-----------------------|

| C0G <10pF       | C0G ≥10pF | X7R          |

|-----------------|-----------|--------------|

| $H \pm 0.05 pF$ | F ± 1%    | J ± 5%       |

| $B \pm 0.1pF$   | G ± 2%    | K ± 10%      |

| $C \pm 0.25 pF$ | J ± 5%    | $M~\pm~20\%$ |

| D $\pm$ 0.5pF   | K ± 10%   |              |

| F ± 1.0pF       |           |              |

#### Dielectric Code

| 1206 J 500 | 0682 | K | X | Η |

|------------|------|---|---|---|

|------------|------|---|---|---|

| Class I              | Class II             |

|----------------------|----------------------|

| A - COG to AEC-Q200  | B - 2X1 (BX)         |

| C - C0G              | D - X7R to IECQ-CECC |

| F - COG to IECQ-CECC | E - X7R to AEC-Q200  |

| Q – High Q           | N - X8R              |

|                      | P - X5R              |

|                      | R - 2C1 (BZ)         |

|                      | X - X7R              |

#### Packaging

|  | ing | 1206 | J | 500 | 0682 | K | Χ | T |  |

|--|-----|------|---|-----|------|---|---|---|--|

|--|-----|------|---|-----|------|---|---|---|--|

'T' is taped and reeled on 178mm (7") reels

'R' is taped and reeled on 330mm (13") reels

'B' is bulk packed in tubs

For further information or technical assistance please contact our Sales Department on: +44 (0)1603 723310 or by email at <a href="mailto:SyferSales@knowles.com">SyferSales@knowles.com</a>

Knowles (UK) Limited, Old Stoke Road, Arminghall, Norwich, Norfolk, NR14 8SQ, United Kingdom

Tel: +44 (0) 1603 723300 Tel. (Sales): 01603 723310 Fax: +44 (0) 1603 723301 Email: <u>SyferSales@knowles.com</u>

Web: www.knowlescapacitors.com/syfer

# FlexiCap™ Termination

"An alternative termination material specifically designed to absorb greater levels of mechanical stress thereby reducing capacitor failures associated with mechanical cracking"

| FlexiCap <sup>™</sup> Introduction         | 2  |

|--------------------------------------------|----|

| Queens Award for Innovation                |    |

| Benefits of Using FlexiCap <sup>™</sup>    | 4  |

| Customer Assembly Process Requirements     | 5  |

| FlexiCap <sup>™</sup> Test Summary         | 6  |

| Key Electrical Characteristics             | 9  |

| Additional Information                     | 10 |

| Ordering Information – Standard MLCC Range | 11 |

## **FlexiCap<sup>™</sup> Introduction**

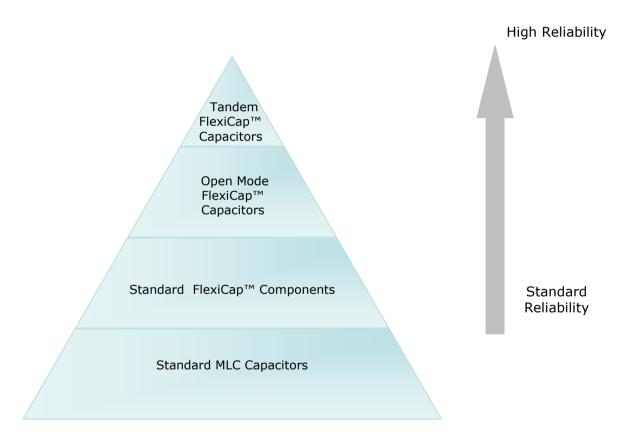

Syfer Technology Ltd introduced FlexiCap $^{\text{\tiny TM}}$  in 1999 and became the first multilayer capacitor manufacturer to offer a flexible termination to customers. This type of termination has proven to be very successful as customers realize the benefits and also as demonstrated by other capacitor manufacturers subsequently introducing flexible terminations, some with very similar names to FlexiCap $^{\text{\tiny TM}}$ .

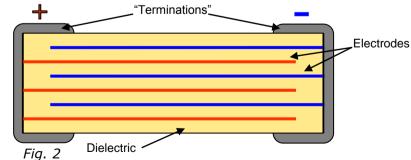

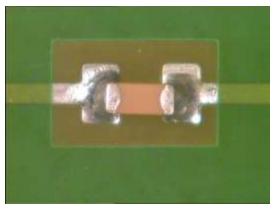

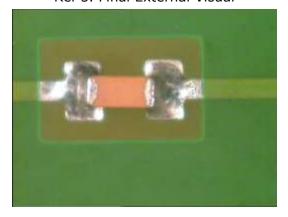

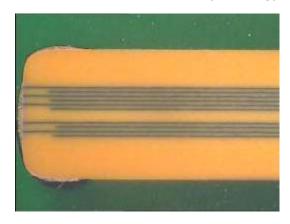

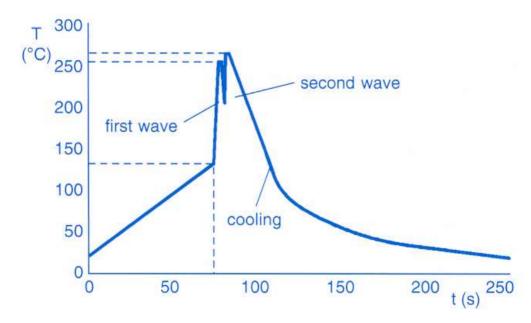

FlexiCap<sup>™</sup> refers to the termination material that is applied over the electrodes. This material is a silver loaded epoxy polymer that is applied using conventional termination techniques and then cured at 180°C. Following the curing process, components are processed through the same manufacturing, test and inspection stages when compared with the more traditional sintered terminated products.

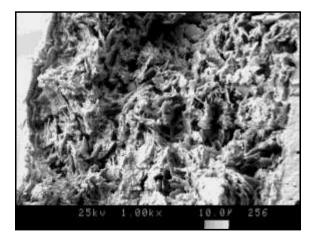

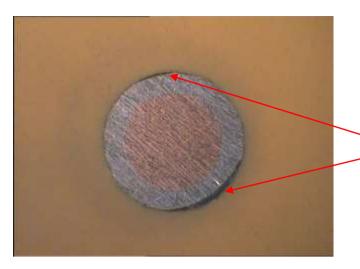

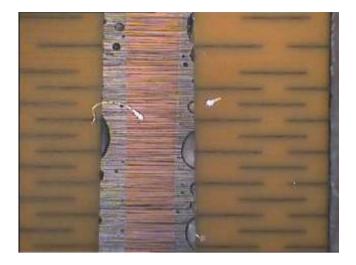

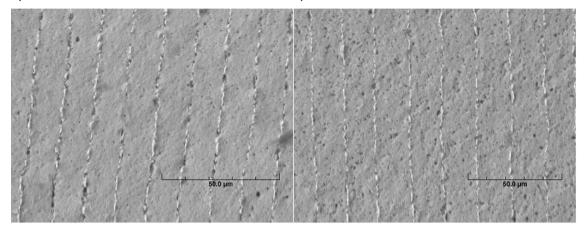

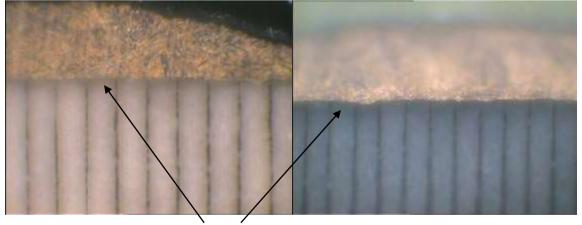

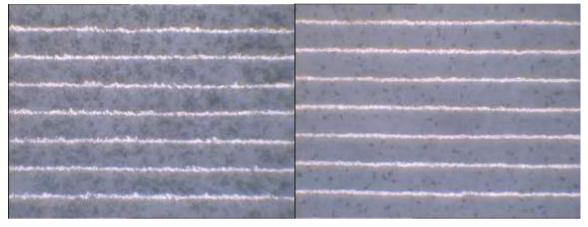

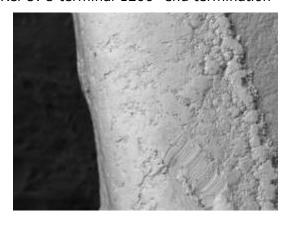

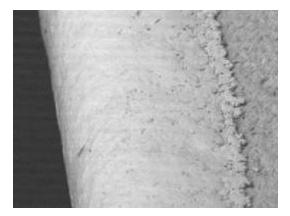

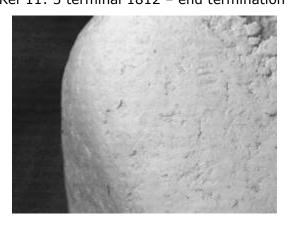

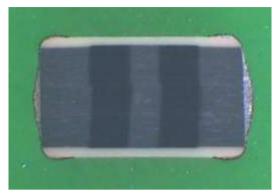

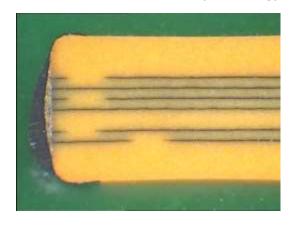

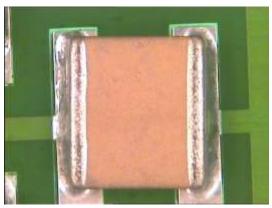

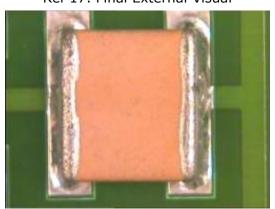

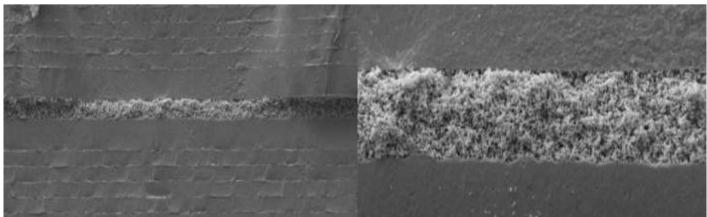

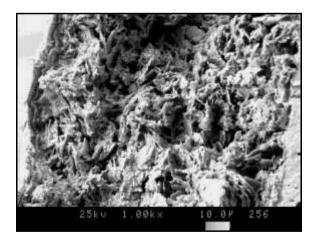

Picture taken at 1000x magnification using a SEM showing a fracture section through a capacitor termination.

The picture demonstrates the fibrous nature of the FlexiCap  $^{\text{TM}}$  termination that absorbs greater levels of mechanical stress when compared with standard sintered silver termination.

Page 3 of 11

#### **Queens Award for Innovation**

The Queen's Awards for Enterprise are the UK's most prestigious awards for business performance. The Awards are presented in three categories: International Trade, Innovation and Sustainable Development

The Awards are made each year by The Queen, on the advice of the Prime Minister, who is assisted by an Advisory Committee that includes representatives of UK Government, industry and commerce, and the trade unions.

The Queens Award for Innovation recognizes companies that have demonstrated commercial success through innovative products or services.

Her Majesty The Queen conferred the Queens Award for Innovation upon Syfer Technology Ltd in 2008 for recognition of outstanding achievements in Innovation with respect to FlexiCap $^{\text{TM}}$ .

Page 4 of 11

### **Benefits of Using FlexiCap**<sup>™</sup>

Sintered termination materials are fired onto the ceramic body of the component at approximately 800°C. The result is a very hard material that provides minimal protection to the ceramic body of the component with respect to mechanical strain when the component is situated on an assembly.

FlexiCap $^{^{\top}}$  termination material is a silver loaded epoxy polymer that is flexible and absorbs some of the mechanical strain between the PCB and the ceramic component. Components terminated with FlexiCap $^{^{\top}}$  withstand greater levels of mechanical strain when compared with sintered terminated components

Types of mechanical strain where  $FlexiCap^{m}$  terminated capacitors offer enhanced protection include mechanical cracking (which is the largest cause for ceramic component failure) and also in applications where rapid temperature changes can occur.

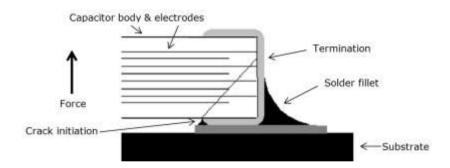

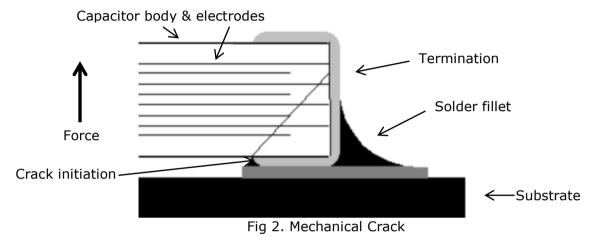

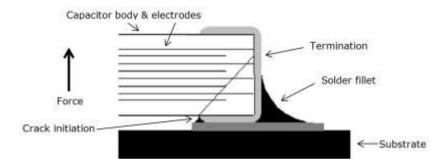

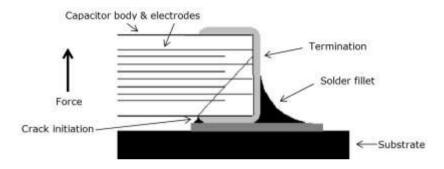

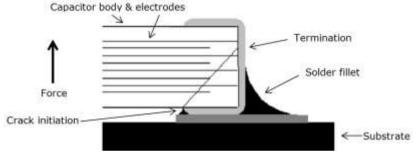

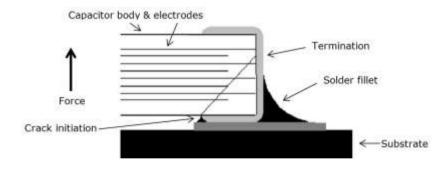

#### Mechanical Cracking

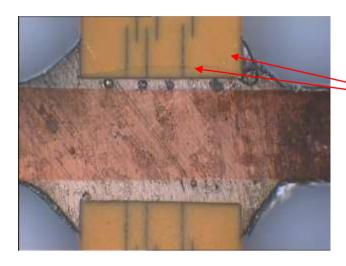

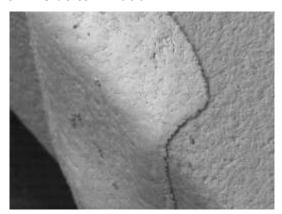

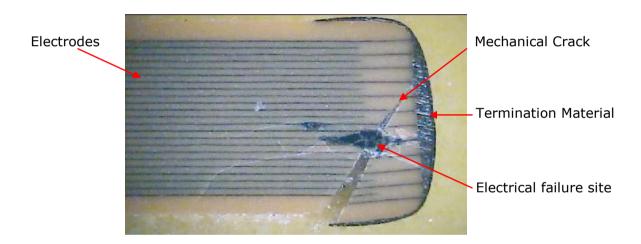

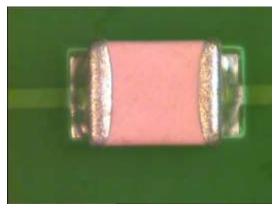

Due to its brittle nature, multilayer ceramic capacitors are more prone to excesses of mechanical stress than other components used in surface mounting. One of the most common causes of capacitor failures is directly attributable to bending of the printed circuit board (PCB) after solder attachment. Excessive bending will create mechanical crack(s) within the ceramic capacitor. Mechanical cracks, depending upon severity, may not cause capacitor failure during the final assembly test. Over time moisture penetration into the crack can cause a reduction in insulation resistance and eventual dielectric breakdown leading to capacitor failure in service.

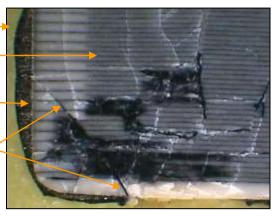

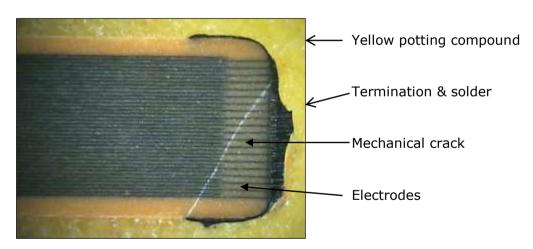

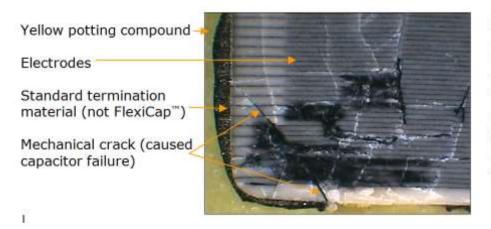

Fig 1. Mechanical Crack

# Application Note Reference No. AN0001 – FlexiCap $^{\text{TM}}$ Issue 10

Page 5 of 11

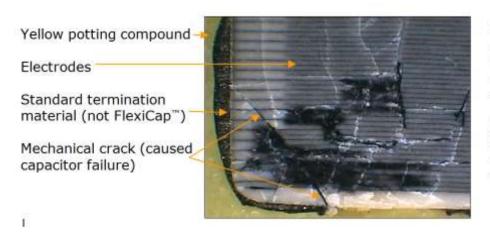

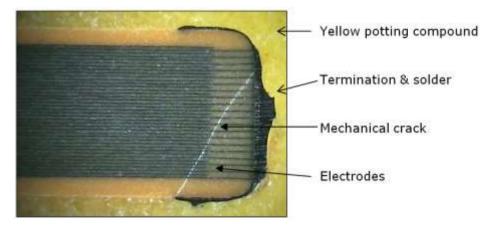

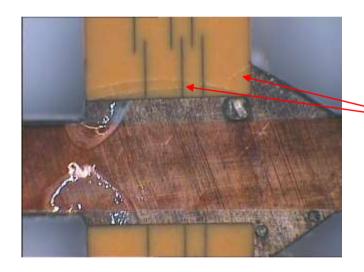

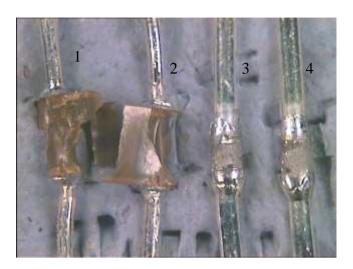

Example of a capacitor issued by a customer to Syfer for failure investigation:

Yellow potting compound-

Electrodes

Standard termination material (not  $FlexiCap^{TM}$ )

Mechanical crack (caused capacitor failure)

Black areas are damaged sections within the capacitor caused during the electrical failure

White lines are thermal cracks created during the electrical failure

#### Temperature Cycling

Rapid temperature changes when components are mounted on a PCB can induce stress as a result of different material CTE (Coefficient of Thermal Expansion) rates. For example, a sintered terminated component will typically fail a temperature cycle test consisting of 1000 cycles (-55°C to 125°C). The difference in material (PCB, ceramic, solder) expansion rates can induce cracks within components that cause components to electrically fail.

FlexiCap<sup> $^{\text{TM}}$ </sup> termination absorbs some of the strain created during repeated rapid temperature changes and components terminated with FlexiCap<sup> $^{\text{TM}}$ </sup> pass temperature cycle tests such as 1000 cycles (-55°C to 125°C).

#### **Customer Assembly Process Requirements**

FlexiCap $^{\text{\tiny TM}}$  terminated capacitors should be handled, stored and transported in the same manner as sintered terminated capacitors. The requirements for mounting and soldering FlexiCap $^{\text{\tiny TM}}$  terminated capacitors are the same as for sintered terminated capacitors.

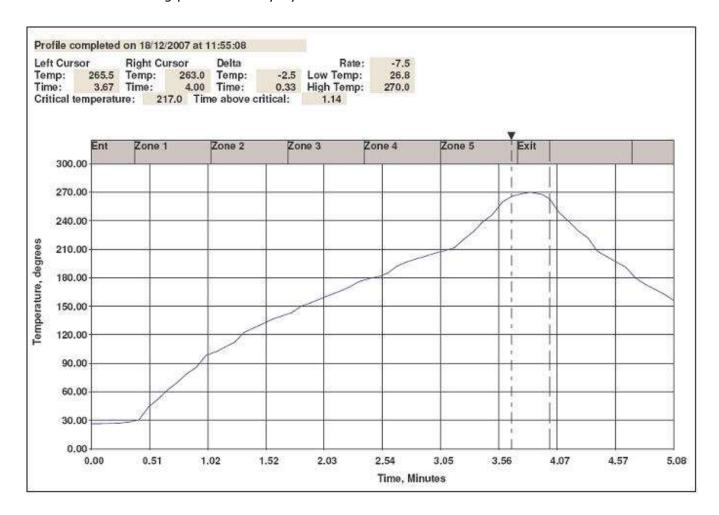

FlexiCap $^{\text{\tiny TM}}$  components are compatible with lead solder applications and lead-free solder applications with a maximum recommended reflow temperature of 270°C.

FlexiCap<sup>™</sup> Moisture Sensitivity Level (MSL) = 1.

Page 6 of 11

## **FlexiCap<sup>™</sup> Test Summary**

FlexiCap<sup>™</sup> has been rigorously tested and approved/ qualified to the following test requirements:

- Syfer qualification and ongoing routine tests.

- IECQ-CECC QC32100 approval.

- TUV Safety Capacitor approvals.

- UL Safety Capacitor approvals.

- AEC-Q200 qualification.

The key tests with respect to FlexiCap<sup>™</sup> performance are as follows.

Bend Test (Board Flex).

Method: Capacitor samples mounted onto a 100mm FR4 Test PCB and subjected to bend testing in accordance with IEC 60068-2-21. Environmental testing: Test U: Robustness of terminations and integral mounting devices or AEC-Q200-005.

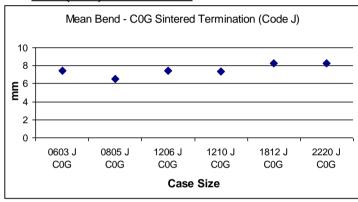

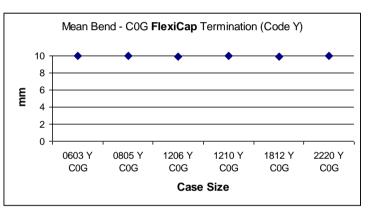

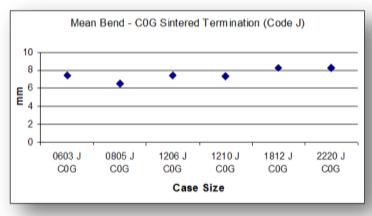

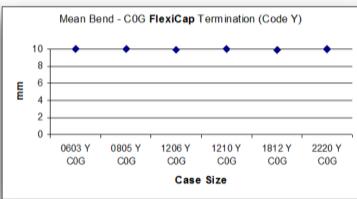

#### COG (NPO) Performance

(10mm maximum bend test equipment capability)

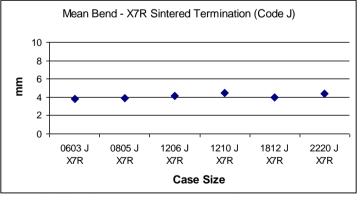

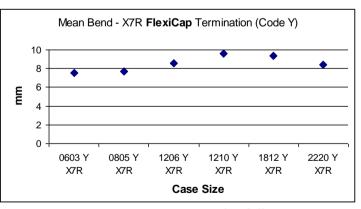

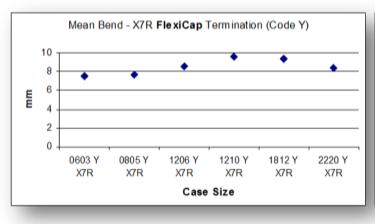

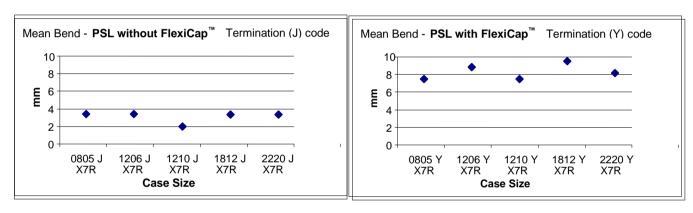

#### X7R Performance

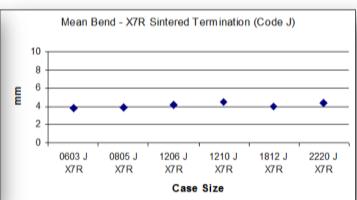

The bend test summary provides a comparison between component case sizes in the following groups:

- COG (NPO) dielectric material with sintered termination material.

- COG (NPO) dielectric material with FlexiCap<sup>™</sup> termination material.

- X7R dielectric material with sintered termination material.

- X7R dielectric material with FlexiCap<sup>™</sup> termination material.

The bend tests conducted confirm that the  $FlexiCap^{^{\text{TM}}}$  termination withstands greater mechanical strain when compared with sintered termination materials.

Page 7 of 11

Load (Life) Tests

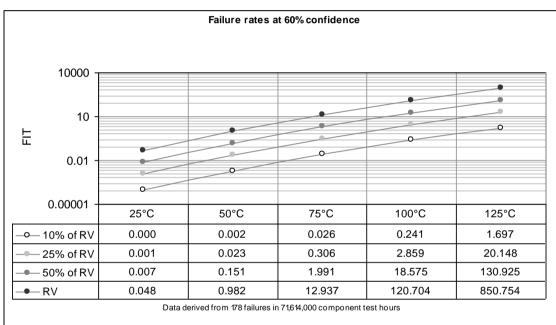

Product type: FlexiCap<sup>™</sup> X7R components

Time period analyzed: 11<sup>th</sup> June 2001 to 11<sup>th</sup> June 2009.

Test laboratory: Syfer Technology Reliability Test Department.

Number of components tested: 71,614

Endurance test conditions: 1000 hours with  $1.5x^{(1)}$  rated voltage applied at  $125^{\circ}$ C. Results: 178 failures in 71,614,000 component test hours.

#### Notes:

1). 1.5x rated voltage used during Syfer routine reliability tests. AEC-Q200 and IECQ-CECC require 1.0x rated voltage. Product specific reliability data available on request.

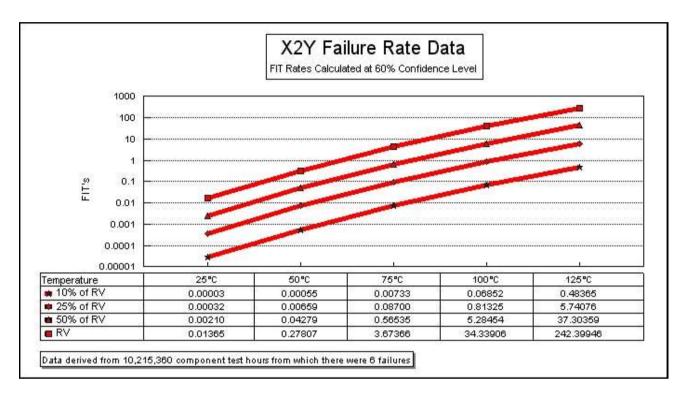

The FIT (Failure In Time) rate graph provides an indication of component reliability in relation to a customer's application with respect to temperature and voltage being applied. For example, at 25°C and 50%RV (Rated Voltage), the FIT rate graph indicates 0.007 FITs. As a comparison, an automotive customer specifies maximum of 0.1 FITs at 25°C and 50%RV (Rated Voltage).

#### Termination Bend Performance - Endurance Testing

A sample of FlexiCap $^{\text{TM}}$  terminated X7R capacitors has been subjected to 20,000 hours at 125°C. Tests conducted after 20,000 hours indicated no deterioration in the electrical or mechanical performance of the FlexiCap $^{\text{TM}}$  termination.

A sample of FlexiCap $^{\text{\tiny TM}}$  terminated X8R capacitors has been subjected to 5,000 hours at 150°C. Tests conducted after 5,000 hours indicated no deterioration in the electrical performance.

#### Humidity Tests

From June 2001 to June 2009, a total of 27194 components (4,568,592 component test hours) have been tested at 85°C @ 85RH for either 168hours or 1000hours. There have been 3 failures that have not been attributed to  $FlexiCap^{TM}$ .

# Application Note Reference No. AN0001 – FlexiCap $^{\text{TM}}$ Issue 10

Page 8 of 11

In addition to the Syfer routine and AEC-Q200 tests, samples have been tested by an external test laboratory for IECQ-CECC Damp Heat Steady State periodic test (56 days 40°C/ 93%RH with applied voltages of 0Vdc, 5Vdc or 50Vdc). Samples pass this test requirement.

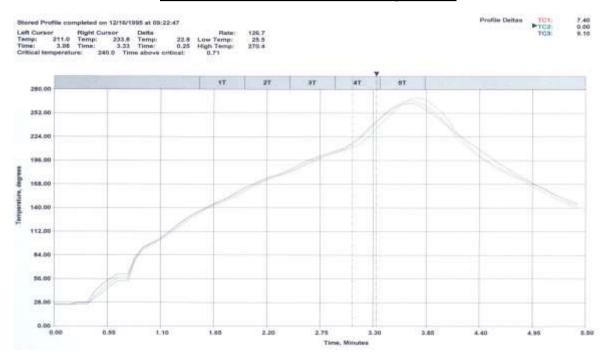

#### Temperature Cycling

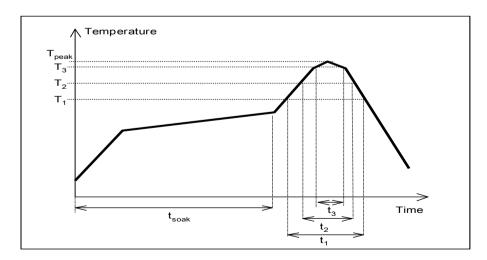

Temperature Cycle Profile: 40-minute cycle consisting of 10 minute ramp and 10 minute dwell at temperature extremes.

Temperature Extremes: -55°C to +125°C.

Number of Cycles: 1000.

Method: Samples of FlexiCap<sup>™</sup> terminated capacitors were soldered onto FR4 test PCB's and

subjected to temperature cycling. After 1000 cycles, the capacitors were sectioned

mounted on the test PCBs for internal visual examination.

Results: There were no cracks within the capacitors.

#### Passive Flammability Test

Method: A sample of FlexiCap<sup>™</sup> terminated capacitors were subjected to a needle flame test

in accordance with IEC 60384-1.

Requirement: Burning droplets of glowing parts falling down shall not ignite the tissue paper

(placed underneath the specimen being tested).

Results: The sample passed the Passive Flammability Test.

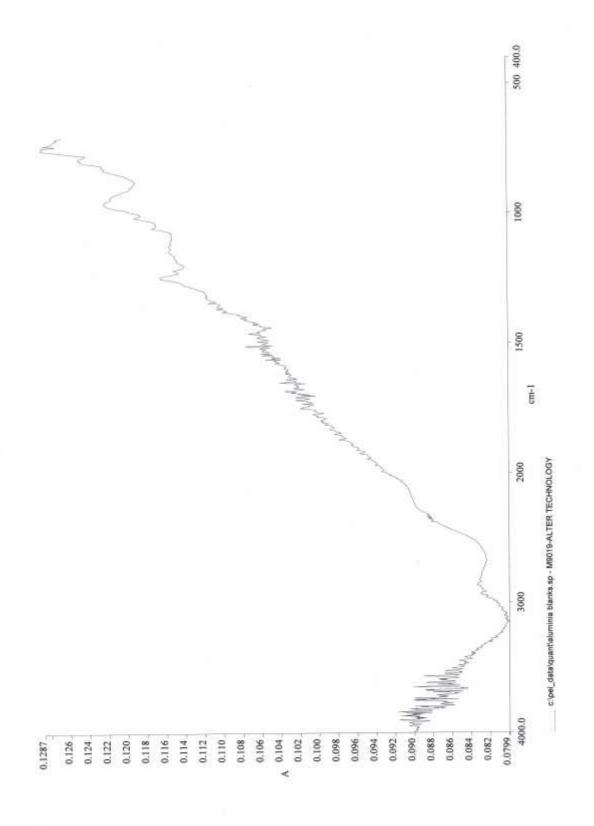

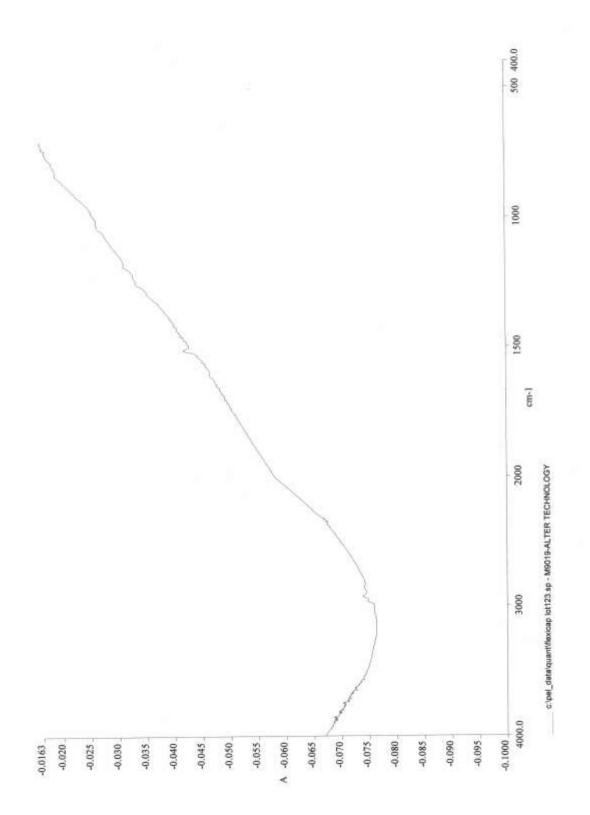

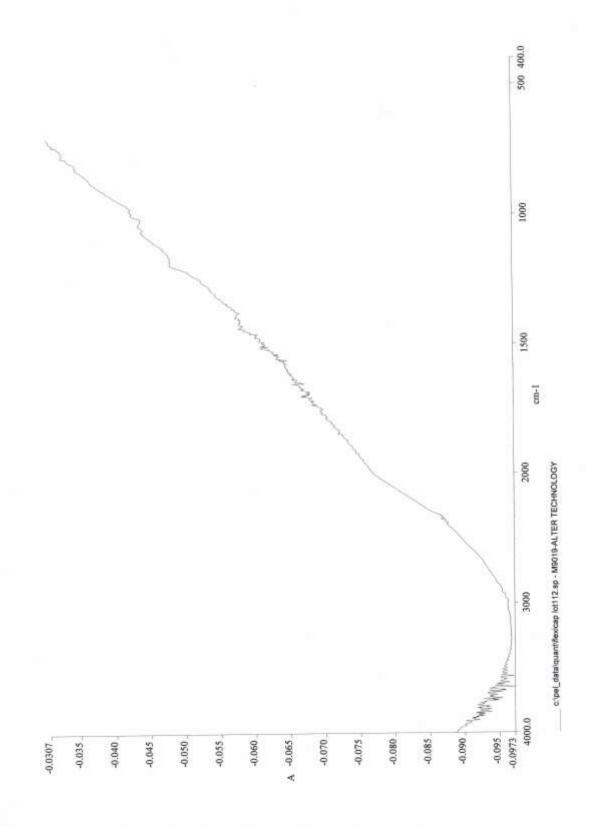

#### Thermal Vacuum Outgassing Test

FlexiCap<sup>™</sup> material successfully passed ECSS-Q-70-02A Thermal vacuum outgassing test for the screening of space materials. The test was conducted by an external test laboratory and results are available in Syfer application note AN0026.

#### Customer Qualification

Samples of FlexiCap<sup>™</sup> terminated capacitors have been supplied to customers for qualification.

The qualifications conducted by customers have been successful and customer reaction to  $\mathsf{FlexiCap}^\mathsf{TM}$  termination has been extremely favorable. Demand for  $\mathsf{FlexiCap}^\mathsf{TM}$  terminated capacitors continues to increase as customers realize the advantages provided.

FlexiCap<sup>™</sup> terminated capacitors are supplied to many blue chip companies, O.E.M's, E.M.S's and international component distributors. Applications include telecoms, military, aerospace, automotive, industrial and power supplies.

## **Key Electrical Characteristics**

$\mathsf{FlexiCap}^{^\mathsf{m}}$  terminated capacitors have equivalent electrical characteristics when compared with sintered terminated capacitors.

For example (type 1812 100nF):

|                                      | Capacitance<br>@ 1kHz | DF @ 1kHz | Resonant<br>Frequency<br>(RF) | Inductance<br>@ RF |

|--------------------------------------|-----------------------|-----------|-------------------------------|--------------------|

| Sintered<br>Termination              | 100.02nF              | 0.01167   | 14.468MHz                     | 1.1965nH           |

| FlexiCap <sup>™</sup><br>Termination | 101.14nF              | 0.01173   | 14.468MHz                     | 1.2099nH           |

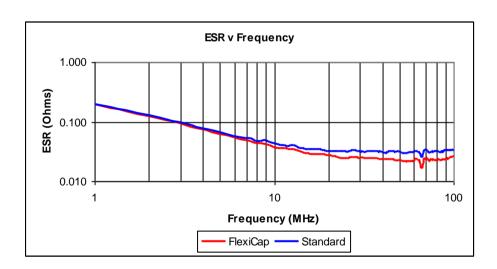

The ESR characterisation of an 18nF 1825 X7R capacitor was undertaken to a frequency of 100MHz. FlexiCap $^{\text{\tiny M}}$  and sintered termination were tested in parallel to determine the relative ESR performance. From the graph below it can be seen that there is a reduction in ESR at high frequencies when capacitors are terminated using FlexiCap $^{\text{\tiny M}}$  termination.

Application Note Reference No. AN0001 – FlexiCap $^{\text{TM}}$  Issue 10

Page 10 of 11

### **Additional Information**

Syfer has generated a comprehensive range of application notes (available at <a href="https://www.knowlescapacitors.com/syfer">www.knowlescapacitors.com/syfer</a>) to provide additional information to customers.

Application notes that provide additional information with respect to FlexiCap<sup>™</sup>:

| APPLICATION NOTE                                                                         | CONTENTS                                                                                                     |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| AN0002 Bend Testing                                                                      | Test methods for Capacitor bend testing, and the shape of typical cracks                                     |

| AN0005 Mechanical Cracking                                                               | Potential causes of mechanical cracking, corrective actions and depanelisation methods                       |

| AN0006 Dielectric Ageing                                                                 | Capacitor dielectric ageing                                                                                  |

| AN0009 AEC-Q200 Stress Test Qualification                                                | Provides information on tests performed by Syfer in accordance with the AEC-Q200 specification               |

| AN0010 Lead-free soldering and bend test performance                                     | The effects of Lead-free soldering on bend testing through solder choice                                     |

| AN0019 Tin Whiskers                                                                      | Tin Whiskers mitigation and surface mount chip capacitors                                                    |

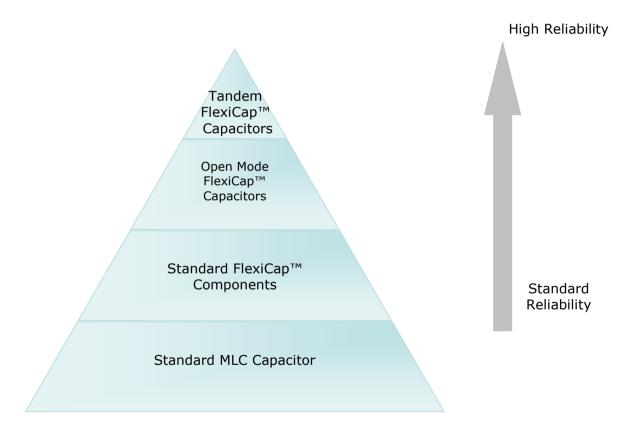

| AN0021 Tandem Capacitors                                                                 | Tandem capacitors terminated with FlexiCap™ provide an ultra robust and reliable component.                  |

| AN0022 Open Mode Capacitors                                                              | Open mode capacitors terminated with FlexiCap™ provide a robust component that fail in an open circuit mode. |

| AN0024 Moisture Sensitivity Level Classification for Syfer products                      | MSL classification IPC / JEDEC J-STD-020D for Syfer products.                                                |

| AN0026 Outgassing test results for FlexiCap™ capacitors                                  | Results for ECSS-Q-70-02A outgassing tests on FlexiCap $^{\text{TM}}$ capacitors.                            |

| AN0028 Soldering / Mounting Chip Capacitors,<br>Radial Leaded Capacitors and EMI Filters | This gives guidance to engineers and board designers on mounting and soldering Syfer products.               |

# Application Note Reference No. AN0001 – FlexiCap $^{\text{TM}}$ Issue 10

Page 11 of 11

## <u>Ordering Information – Standard MLCC Range</u>

For quotations please contact Syfer Sales Department <a href="mailto:SyferSales@knowles.com">SyferSales@knowles.com</a>.

Knowles (UK) Limited, Old Stoke Road, Arminghall, Norwich, Norfolk, NR14 8SQ, United Kingdom

Tel: +44 (0) 1603 723300 Tel. (Sales): 01603 723310 Fax: +44 (0) 1603 723301 Email: <u>SyferSales@knowles.com</u>

Web: www.knowlescapacitors.com/syfer

# **Bend Testing**

## Methods and International Specifications

| Introduction                                    | 2 |

|-------------------------------------------------|---|

| International Requirements/ Specifications      | 2 |

| Capacitor Bend Tests Conducted on Syfer Product | 3 |

| Mechanical Crack Shape                          | 7 |

| Summary                                         | 8 |

Page 2 of 8

## **Introduction**

Due to its brittle nature, multilayer ceramic capacitors are more prone to excesses of mechanical stress than other components used in surface mounting. One of the most common causes of capacitor failures is directly attributable to the bending of the printed circuit board (PCB) after solder attachment. Excessive bending will create mechanical stress within the ceramic capacitor that, if sufficient, can result in mechanical cracks.

The purpose of this report is to provide details regarding:

- International Specifications that define bend test methods and acceptability.

- Methods employed by Syfer to measure the mechanical performance of the termination material.

- The shape of cracks created by PCB bending mechanical stress.

#### **International Requirements/ Specifications**

The international requirement for bend testing is referred to in several different specifications.

- 1. IEC 60384-1:2001 Fixed capacitors for use in electronic equipment Part 1: Generic Specification section 4.35 Substrate bending test refers to IEC 60068-2-21.

- 2. IEC 60068-2-21: 2006 Environmental testing: Test U: Robustness of Terminations and Integral Mounting Devices. Section 8 test Ue specifies the test required to assess the mechanical robustness of surface mounting device terminations when mounted on a substrate. Test Ue<sub>1</sub> specifies the substrate bend test.

The purpose of test Ue<sub>1</sub> is to verify that the capacitors can withstand bending loads that are likely to be applied during normal assembly or handling operations.

IEC 60068-2-21 refers to requirements such as deflection and acceptance criteria as being included in the "relevant specification". Syfer maintains IECQ CECC (International Electrotechnical Commission Quality certification programme- CENELEC Electronic Components Committee) product approval and the "relevant specification" is QC 32100-A001:2007.

3. QC 32100-A001:2007 Table 2 - Periodic Tests defines board flex minimum requirements as:

COG: All types, X7R: Y and H only (Flexicap™)

- 3mm deflection Class I

- 2mm deflection Class II

- X7R (non Flexicap<sup>™</sup> termination) 1mm deflection

- 4. AEC-Q200-005, Board Flex / Terminal Bond Strength Test.

Minimum requirements stated in table 2 stress test reference 21: 2mm (min) for all except 3mm for Class I.

Page 3 of 8

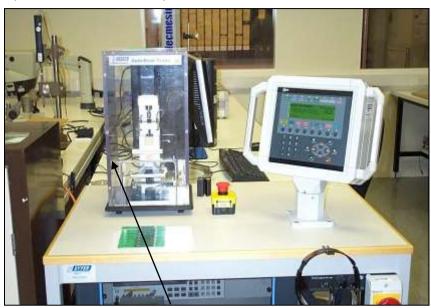

#### **Capacitor Bend Tests Conducted on Syfer Product**

Currently there are 2 methods employed by Syfer to measure the mechanical performance of capacitor termination when mounted on a substrate:

#### 1. External Test Laboratory

To maintain IECQ-CECC product approval (certified by BSI "British Standards Institute") Syfer issues capacitor samples to an external test laboratory for a variety of tests to be conducted in accordance with IECQ CECC requirements. The external test laboratory is not part of Syfer and has full traceability to International Reference Standards.

Syfer has maintained IECQ-CECC product approval for >20 years.

#### 2. Syfer Bend Tests

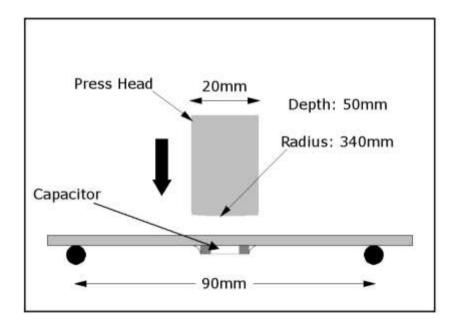

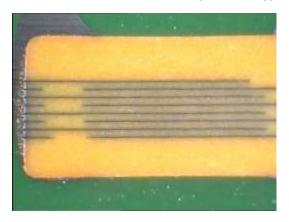

In addition to the external test laboratory Syfer also conducts bend tests. Samples of capacitors are mounted onto FR4 Test PCBs using 62/36/2 Sn/Pb/Ag solder and subjected to bend testing in accordance with IECQ CECC or AEC –Q200-005 (depending on termination and dielectric types.

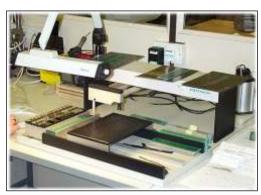

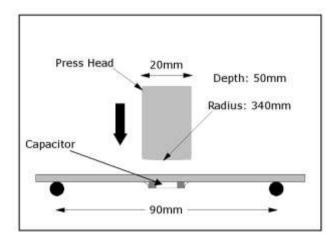

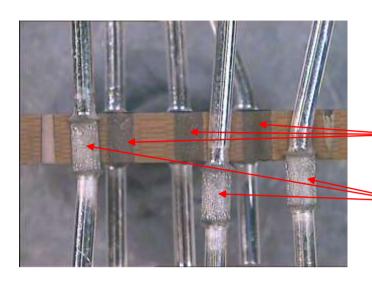

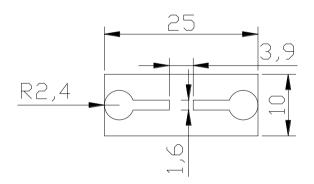

Example of FR4 Test PCB Used

Capacitor Placement Method

Syfer's Bend Test Facility

Fig 1. Bend Test Method

Page 5 of 8

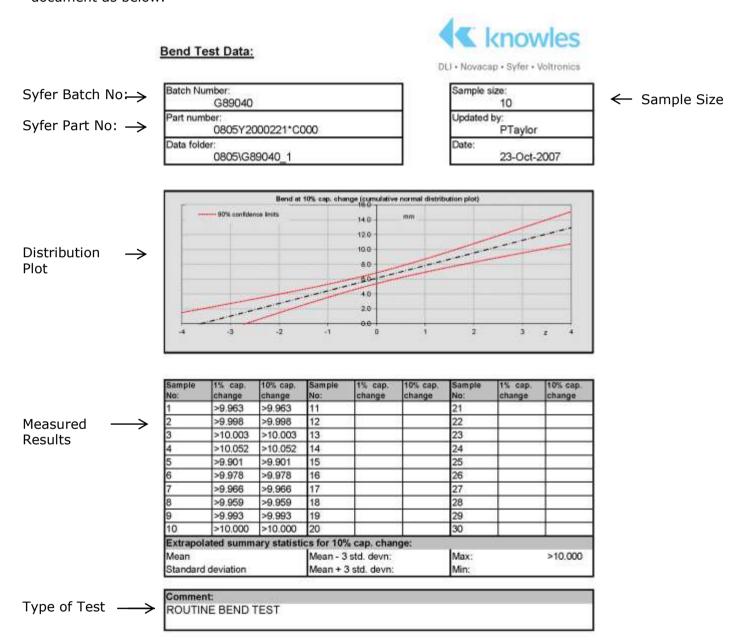

A minimum of 10 Test PCBs (depending on test requirements) are used for each bend test. Each PCB is mounted with one capacitor and deflected automatically until the capacitor breaks. The software analyses the change in capacitance measured by the Agilent 4288A capacitance meter. As soon as the capacitance change is greater than 10% the bend is recorded in mm.

The results of the test are saved to the Syfer network but also can be communicated as a printed document as below.

#### knowles Bend Test Data: DLI · Novacap · Syfer · Voltronics Syfer Batch No: → Batch Number: Sample size: ← Sample Size 10 Updated by Syfer Part No: -0805Y2000221\*C000 PTaylor Date: 0805\G89040\_1 23-Oct-2007 12.0 Distribution Plot -> 10.0 8.0 28 change change >9.963 >9.963 11 21 22 Measured Results→2 >9.998 >9.998 12 23 >10.003 >10.003 13 >10.052 >10.052 14 24 >9.901 >9.901 15 25 9.978 >9,978 16 26 27 >9.966 >9.966 17 >9.959 >9.959 18 28 >9.993 >9.993 19 29 10 >10.000 >10.000 30 20 Extrapolated summary statistics for 10% cap, change: Mean Mean - 3 std devn Max: >10 000 Standard deviation Mean + 3 std. devn: Comment: Type of Test ROUTINE BEND TEST

Document shows the results for Flexicap™ terminated components

Page 6 of 8

#### Bend Test Performance Summary

#### COG (NPO) Performance

(10mm maximum bend test equipment capability)

#### X7R Performance

The bend test summary provides a comparison between component case sizes in the following groups:

- COG (NPO) dielectric material with sintered termination material.

- COG (NPO) dielectric material with FlexiCap™ termination material.

- X7R dielectric material with sintered termination material.

- X7R dielectric material with FlexiCap™ termination material.

The bend tests conducted confirm that the  $\mathsf{FlexiCap}^{^\mathsf{m}}$  termination withstands greater mechanical strain when compared with sintered termination materials.

Page 7 of 8

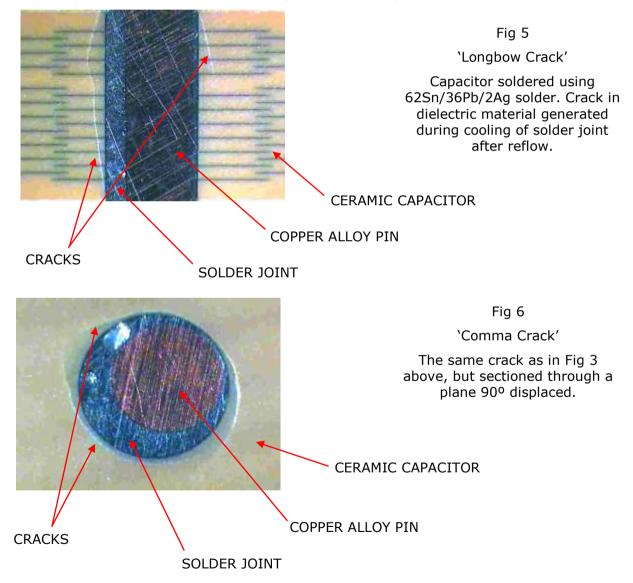

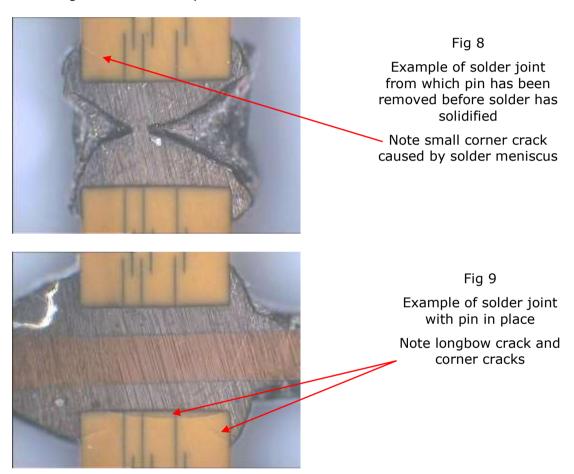

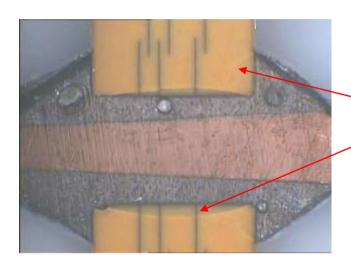

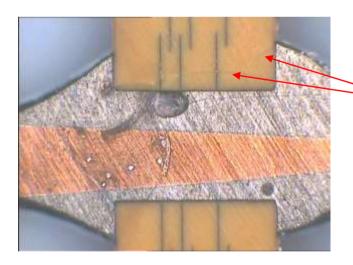

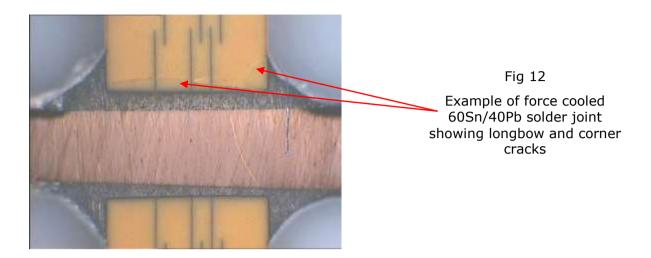

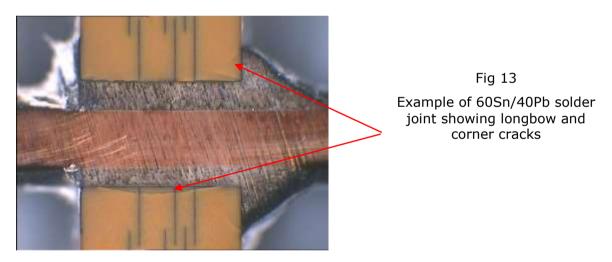

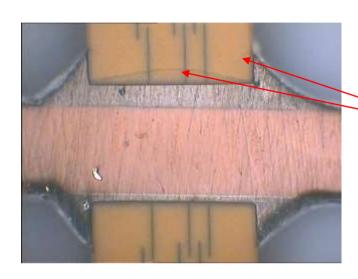

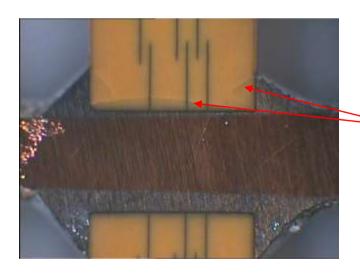

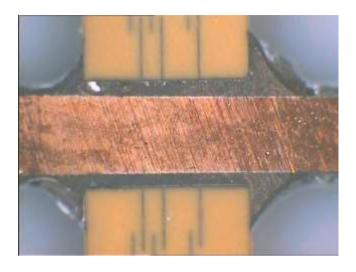

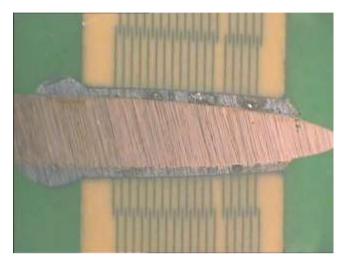

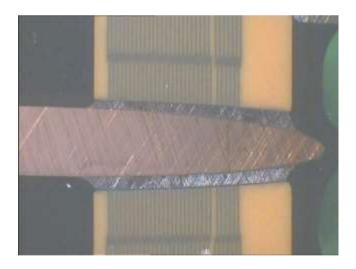

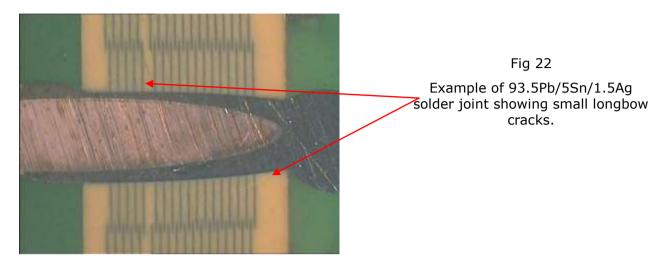

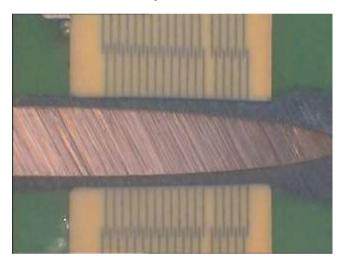

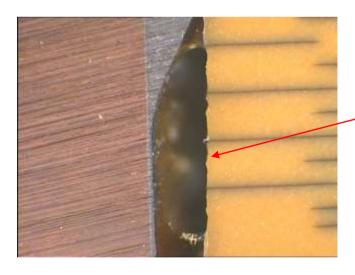

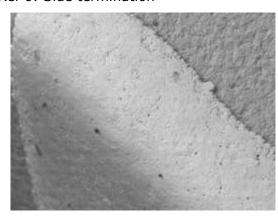

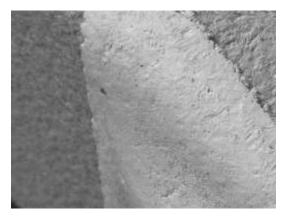

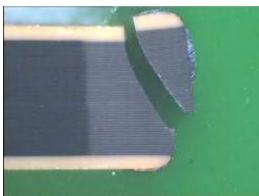

### **Mechanical Crack Shape**

By conducting extensive bend testing capacitor manufacturers including Syfer have demonstrated that mechanical stress applied by bending the PCB results in a distinctive type of crack within the capacitor.

During Syfer's investigation into mechanical cracking over 15000 capacitors were subjected to bend testing.

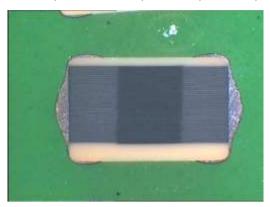

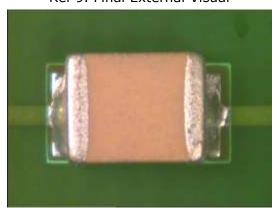

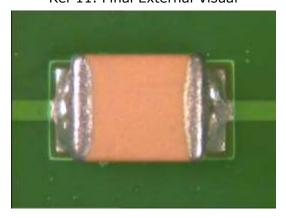

Example of capacitors issued by customers to Syfer for failure investigation:

Page 8 of 8

#### **Summary**

- Syfer capacitors pass the International Specifications for bend testing. In addition to routine tests conducted at Syfer an external test laboratory conducts periodic IECQ CECC tests on Syfer product including bend testing.

- The crack created by mechanical stress during PCB bending is a distinctive type of crack.

#### For further information regarding:

- a) Potential causes for mechanical cracking refer to Syfer application note "Mechanical Cracking" application note reference AN0005.

- b) Flexicap<sup>™</sup>. Refer to "Flexicap<sup>™</sup> Termination" application note reference AN0001.

- c) AEC-Q200. Refer to "AEC-Q200 Stress Test Qualification for Passive Components" application note reference AN0009.

Information is also available on Syfer's web site www.knowlescapacitors.com/syfer

Knowles (UK) Limited, Old Stoke Road, Arminghall, Norwich, Norfolk, NR14 8SQ, United Kingdom Tel: +44 (0) 1603 723300

Tel. (Sales): 01603 723310 Fax: +44 (0) 1603 723301 Email: <u>SyferSales@knowles.com</u> Web: <u>www.knowlescapacitors.com/syfer</u>

# Quality & Reliability Data

| Section 1 - Introduction         | 2 |

|----------------------------------|---|

| Section 2 - Test Conditions      | 4 |

| Endurance                        | 4 |

| 85°C / 85%RH                     | 4 |

| Section 3 - F.I.T. Rate Data     | 5 |

| Acceleration Factor Calculations | 5 |

| Conversion Factors               | 5 |

| COG Capacitor Reliability Data   | 6 |

| FIT (Failure In Time) Rate Graph | 6 |

| X7R Capacitor Reliability Data   | 7 |

| FIT (Failure In Time) Rate Graph | 7 |

Page 2 of 7

#### **Section 1 - Introduction**

The major influence, within Syfer Technology Limited, is to provide its Customers with 'World Class' capacitors.

Syfer has developed its own unique 'Wet Process' for the manufacture of Multilayer Ceramic Chip Capacitors. This has been in operation for some 30 years, significantly increasing the reliability levels obtained today, over those that were the expectation then.

Syfer's 'Wet Process' is based upon the principle of Screen Printing, both ceramic and electrode layers, in a single operation. This gives a more consistent deposition and greater accuracy of electrode alignment. In contrast to parts made by 'Tape Methods', it reduces stresses within the components.

At all manufacturing stages, well defined controls are in place. Statistical Process Control (SPC) techniques are used extensively to monitor and to reduce process variability.

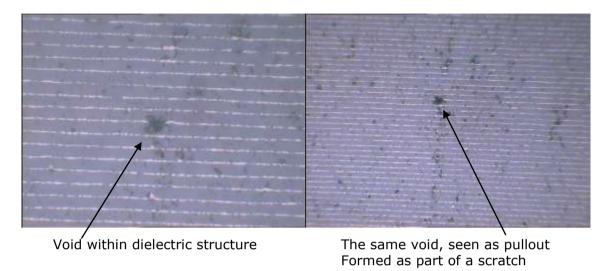

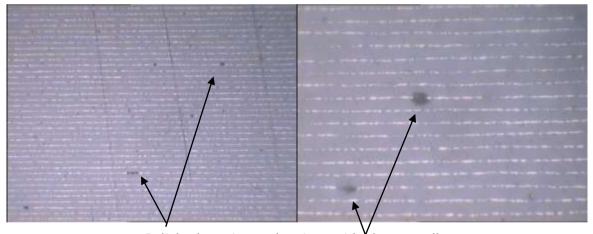

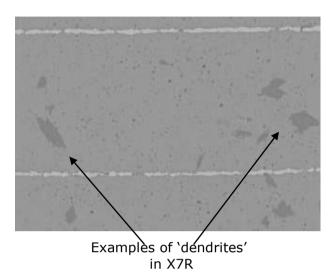

Microsections are prepared from each batch of product built. Destructive Physical Analysis (DPA) is conducted on each microsection to verify structural integrity and the absence of voids, delaminations or other defects.

After the fabrication cycle, 100% testing is conducted for:

- (1) Capacitance

- (2) Dissipation Factor

- (3) Insulation Resistance

- (4) Voltage Proof

Syfer's Quality Control Function audits each process stage and the outgoing products, to ensure strict conformity to internal, customer, national and international specifications.

Syfer holds IECQ-CECC, TUV, UL, ISO9001, ISO14001 and OHSAS18001 approvals.

Page 3 of 7

In addition to its advanced construction methods, and sophisticated Quality Controls, Syfer carries out regular long term accelerated tests on its products to prove their reliability.

The Capacitor Industry accepts that no single test, in isolation, is an effective measure of total reliability and, therefore, accelerated testing, directed at selected capacitor performance factors, is conducted, by Syfer, on a regular basis. This includes:

- (1) 125°C Endurance Testing at 1.5 times rated voltage

- (2) 85°C/85% Relative Humidity Testing at stress voltages of 1.5, 5 and 50 vdc

Syfer maintains its rigorous test regime, to give its customers useful and detailed data on the reliability of its products. There is a continuing trend toward higher value capacitors in all major dielectric categories as circuit designers have demanded even greater volumetric capacity. This has prompted an increase in the number of 'high' value lots tested; now approximately 20% of such parts are tested compared with 10% for standard product. The results presented here reflect this change in product mix.

Each section of this document describes the methodology of test and includes a summary of the results obtained. F.I.T. Rate Data is shown, based upon Endurance Test results.

The aim of this document is to confirm that Syfer continues to maintain its reputation for the manufacture of products that meet, and exceed, customer's expectations of reliability.

Syfer's Quality and Technical personnel are available to discuss this information, on request.

Page 4 of 7

#### **Section 2 - Test Conditions**

Endurance

Duration 1000 Hours

Intermediate Check Time 168 Hours

Voltage 1.5 x Rated Voltage

Current Limitation Each component stressed via a  $100k\Omega$  resistor

Temperature X7R125°C

C0G125°C

Post Test Limits

Insulation Resistance COG  $\geq 4000 M\Omega$  or 40s

$X7R \geq 2000M\Omega \text{ or } 50s$

(whichever is the less)

85°C / 85%RH

Duration 168 Hours

Voltage Bias Rated voltage up to a maximum of 50 volts dc, however, when specified,

1.5Vdc or 5Vdc may be required

Current Limitation Each component stressed via a  $100k\Omega$  resistor

Temperature 85°C Relative Humidity 85%

Post Test Limits

Insulation Resistance  $C0G \ge 4000M\Omega$  or 40s

$X7R \geq 2000M\Omega \text{ or } 50s$

(Whichever is the less)

Page 5 of 7

#### Section 3 - F.I.T. Rate Data

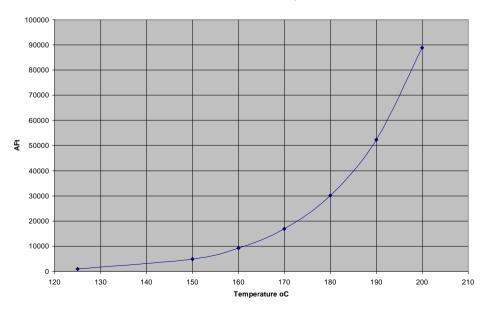

Acceleration Factor Calculations

Acceleration Factor (AF) =

$$AF_{voltage} \times AF_{temperature}$$

where

Acceleration Factor<sub>voltage</sub> =

$$\left[\frac{V_{stress}}{V_{use}}\right]^{2.7}$$

and

Acceleration Factor temperature =

$$e^{\left(\frac{E_a}{k}\left[\frac{1}{T_{use}} - \frac{1}{T_{stress}}\right]\right)}$$

where  $E_a$  = Activation energy (1.0 eV for M.L.C's)

k = Boltzmann' Constant (8.617 x 10<sup>-5</sup>eV/K)

T = Temperature in K (273 + Temperature in  $^{\circ}$ C)

Failure Rates at the Specified Confidence Level (60%) are derived from:

$$FR = \frac{\chi^2}{2} \times \frac{1}{AF \times H}$$

where FR = Estimated Failure Rate at Use Stress

$X^2$  = Chi Square calculated for number of rejects at test stress

H = Component test hours

#### Conversion Factors

| From | То           | Operation                      |

|------|--------------|--------------------------------|

| FITS | MTBF (Hours) | 10 <sup>9</sup> ÷ FITS         |

| FITS | MTBF (Years) | $10^9 \div (FITS \times 8760)$ |

Page 6 of 7

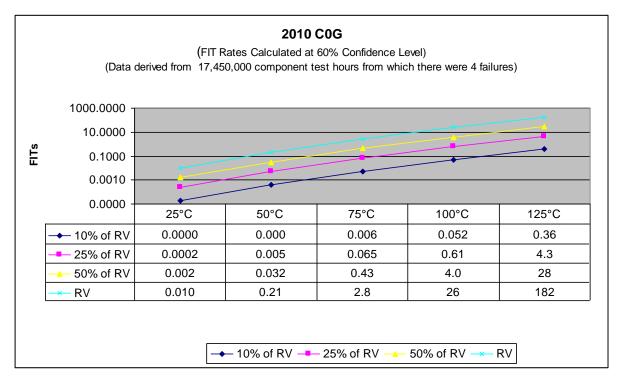

#### COG Capacitor Reliability Data

Product type: C0G capacitors.

Time period analyzed: 1<sup>st</sup> January 2010 to 31<sup>st</sup> December 2010

Test laboratory: Syfer Technology Reliability Test Department

Number tested: 17,450

Test conditions: 1000 hours with 1.5x rated voltage applied at 125°C

Results: 4 failures in 17,450,000 component test hours

#### FIT (Failure In Time) Rate Graph

The FIT (Failure In Time) rate graph provides an indication of component reliability in relation to a customer's application with respect to temperature and voltage being applied. For example, at 25°C and 50%RV (Rated Voltage), the FIT rate graph indicates 0.002 FITs. As a comparison, an automotive customer specifies maximum of 0.1 FITs at 25°C and 50%RV (Rated Voltage).

Page 7 of 7

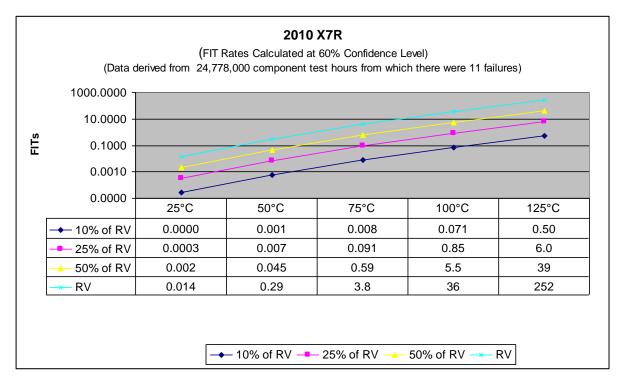

#### X7R Capacitor Reliability Data

Product type: X7R capacitors.

Time period analyzed: 1<sup>st</sup> January 2010 to 31<sup>st</sup> December 2010

Test laboratory: Syfer Technology Reliability Test Department

Number tested: 24,778

Test conditions: 1000 hours with 1.5x rated voltage applied at 125°C Results: 11 failures in 24,778,000 component test hours

#### FIT (Failure In Time) Rate Graph

The FIT (Failure In Time) rate graph provides an indication of component reliability in relation to a customer's application with respect to temperature and voltage being applied. For example, at 25°C and 50%RV (Rated Voltage), the FIT rate graph indicates 0.002 FITs. As a comparison, an automotive customer specifies maximum of 0.1 FITs at 25°C and 50%RV (Rated Voltage).

Knowles (UK) Limited, Old Stoke Road, Arminghall, Norwich, Norfolk, NR14 8SQ, United Kingdom Tel: +44 (0) 1603 723300

Tel. (Sales): 01603 723310 Fax: +44 (0) 1603 723301 Email: <u>SyferSales@knowles.com</u> Web: <u>www.knowlescapacitors.com/syfer</u>

# Mechanical Cracking

The Major Cause for Multilayer Ceramic Capacitor Failures

| Introduction                                | . 2 |

|---------------------------------------------|-----|

| Potential Causes                            | . 3 |

| Exceptional Circumstances                   | . 3 |

| Normal Circumstances                        | . 3 |

| Corrective Actions                          | . 4 |

| Assembly Design/ Manufacture Considerations | . 4 |

| Review Production Processes                 | . 5 |

| Syfer Capacitor Enhancements Offered        | . 6 |

| Test Methods                                | . 6 |

| Depaneling Methods                          | . 7 |

#### Introduction

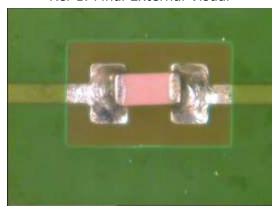

Due to its brittle nature, multilayer ceramic capacitors are more prone to excesses of mechanical stress than other components used in surface mounting. One of the most common causes of capacitor failures is directly attributable to bending of the printed circuit board (PCB) after solder attachment. Excessive bending will create mechanical crack(s) within the ceramic capacitor. Mechanical cracks, depending upon severity, may not cause capacitor failure during the final assembly test. Over time moisture penetration into the crack can cause a reduction in insulation resistance and eventual dielectric breakdown leading to capacitor failure in service.

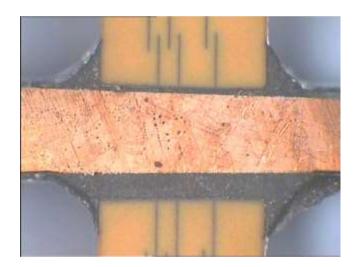

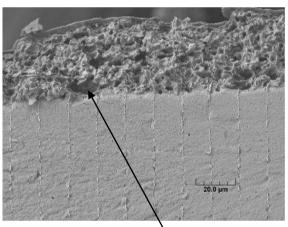

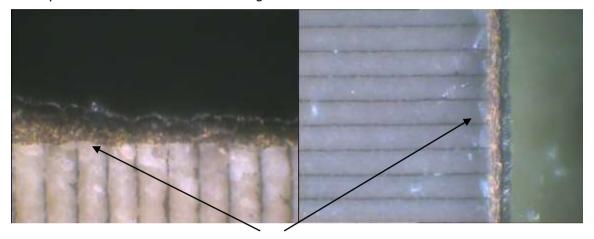

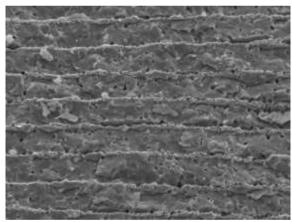

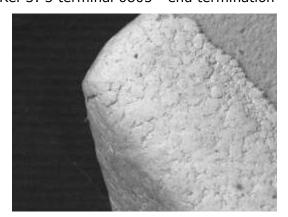

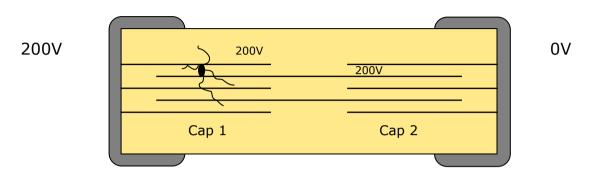

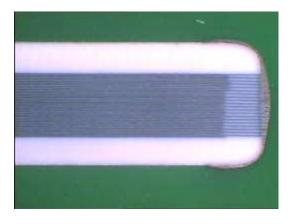

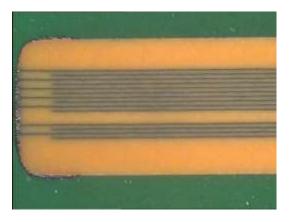

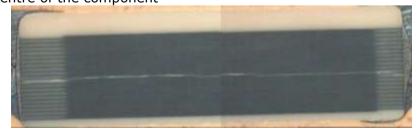

Figure 1: Mechanical Crack

Example of capacitors issued by customers to Syfer for failure investigation:

Black areas are damaged sections within the capacitor caused during the electrical failure

White lines are thermal cracks created during the electrical failure

Page 3 of 7

#### **Potential Causes**

Mechanical cracks are created by excessive mechanical stress after the capacitors have been soldered onto the substrate.

Excessive mechanical stress can be the result of the following:

#### Exceptional Circumstances

• Interference fit. For example, physical abuse.

#### Normal Circumstances

- · Assembly design.

- Board de-paneling causing the PCB to bend.

- Automatic test equipment employing a "bed of nails" as contacts. Faults often occur at, or in close proximity to, support pillars within the test jig. Vacuum fixtures can also cause excessive PCB bend.

- PCB distortion/ warp caused by storage conditions or uneven PCB designs. Frequently distorted PCBs are straightened after the soldering process causing the capacitors to mechanically crack.

- Radial/ through hole component insertion especially if there is a tight fit between the radial leads and PCB hole.

- Attachment of rigid fixtures such as heat sinks.

- Fitting IC's, connectors into solder mounted sockets with no support.

- Methods of transportation/ storage and handling during process stages allowing the PCB to bend.

- Fixing completed sub-assemblies into the final assembly. For example, employing a snap fit operation or by over-tightening fixing screws.

Page 4 of 7

#### **Corrective Actions**

Extensive bend tests performed at Syfer including bench-marking against competitor's products has proven that:

- i. Syfer capacitors pass the International Specifications <sup>(1)</sup> defining robustness of termination criteria.

- ii. the bend test performance of Syfer's sintered termination capacitors is comparable with competitor's sintered termination product.

- (1) For International Specifications and Syfer Bend Test Methods refer to Syfer Application Note AN0002 Bend Testing.

The only effective methods of resolving mechanical cracking issues are:

- i. reduce the mechanical stress being exerted on the capacitors.

- ii. and/ or increasing the process window so that the mechanical stress exerted onto the ceramic section of the capacitor is reduced.

ATE, functional tests and reliability tests have limited success in identifying capacitor failures caused by mechanical cracking.

Assembly Design/ Manufacture Considerations

Mechanical stress can be influenced by a number of different factors associated with the design of the assembly and assembly manufacture. These factors include:

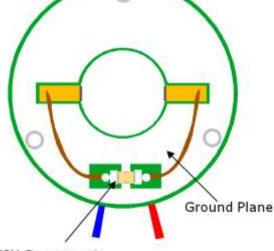

- PCB design copper power and ground planes.

- A PCB design resulting in an uneven metal distribution (usually caused by large power or ground planes) can result in PCB warpage during the soldering process caused by the different Thermal Coefficient of Expansion rates between the copper and the epoxy fiber glass. If large power/ ground planes are required then cross hatching the copper area may prove to be useful.

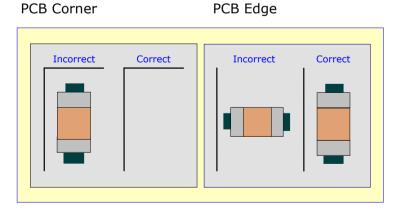

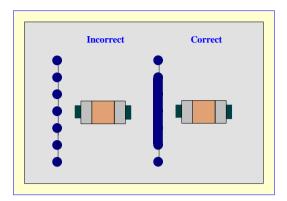

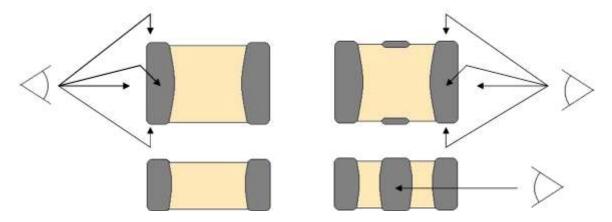

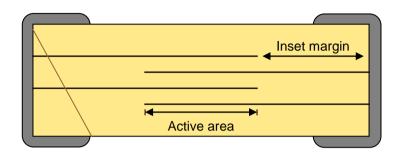

- Position/ orientation of the capacitor on the PCB in relation to the edge of the PCB and other components/ attachments.

Capacitor placement not recommended in the corner of the PCB.

Recommended capacitor orientation with respect to PCB edge (denoted by black lines).

Note: Stress zone is typically within 5mm of PCB edge or fixing point.

Page 5 of 7

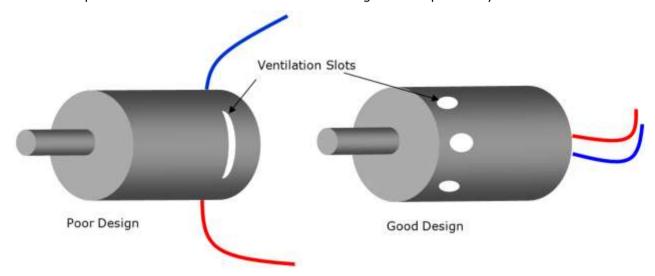

#### Use of PCB slots

Using a slot along the depanelisation edge reduces the level of stress exerted onto the capacitor by approximately 50%.

#### Solder pad/ land sizes

Reducing the pad/ land size can reduce the level of stress exerted onto the capacitor by approximately 50%.

#### Use of Adhesives.

Depending upon the type of adhesive used, the effect can be a significant reduction in the bend strength of a capacitor. For example, during experiments approximately 50% of the PCB bend was required to crack a capacitor fixed with adhesive when compared to a capacitor not fixed with adhesive.

#### Review Production Processes

Mechanical cracking occurs after the capacitors have been soldered into position. Subsequent flexing of the PCB creates mechanical stress within the capacitor that if sufficient can result in the capacitor being mechanically cracked.

When mechanical cracking has been identified as the cause for capacitor failures the typical approach for customers is to review the production process for any obvious process stage including handling and transportation that may be bending the PCB. If no obvious stage is identified then the next step is to remove samples of capacitors from assemblies at different process stages and then subject the capacitors to sectioning/ internal examination to determine if the capacitors have been cracked. The shape of mechanical cracks is shown in Fig.1.

Page 6 of 7

An example of a typical investigation would be to remove capacitors from assemblies after completing the following stages:

- Soldering

- Depanelisation

- Insertion of radial components including connectors and IC's into sockets

- ATE

- Fixing the completed sub-assembly into the final assembly.

#### Syfer Capacitor Enhancements Offered

Syfer offers a polymer termination that effectively reduces the mechanical stress being exerted onto the ceramic section of the capacitor by approximately 50%. The polymer termination is being used by a variety of customers and requires no changes to the customer's assembly process.

For further details refer to Syfer Application Note AN0001 Polymer.

#### Test Methods

There is no 100% guaranteed method for being able to test capacitors that have been mechanically cracked. The success of the tests conducted relies on the extent of the mechanical cracks – wider cracks are more likely to fail.

Examples of tests conducted by customers:

- Dry Heat/ Steady State. Assemblies powered in a hot dry environment to accelerate the breakdown of the capacitors.

- Damp Heat/ Steady State. Assemblies powered in a hot humid environment to try to drive moisture into the crack and cause capacitor failure.

- Temperature Cycling. Assemblies are temperature cycled with the purpose of opening the crack to cause capacitor failure.

- Vibration and Shock. Assemblies are subjected to vibration/ shock tests with the purpose of opening the crack to cause capacitor failure.

- X-Ray. Customers have tried to employ x-ray solder joint inspection equipment to try to detect mechanical cracks with very limited success.

- Scanning Acoustic Microscopy.

The tests conducted have depended upon the equipment available to customers and the success of tests has varied.

Page 7 of 7

#### **Depaneling Methods**

Depaneling is the process of separating individual PCBs from a main panel (usually after the soldering operation) and can present a high risk of mechanically cracking ceramic capacitors. There are various depaneling methods employed, some of which present a greater risk when compared to other methods.

As a guide, depaneling methods include:

| Depaneling Method                    | Benefits                                                                                                                             | Negatives                                                                                                                                           | Comments                                                                                                                       |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Manual Break-Out                     | Flexibility.<br>No tooling costs/ changes.<br>No software set-up.                                                                    | High risk of mechanical cracks. Labour intensive. Not consistent. Potentially high scrap rate.                                                      | Not generally recommended though frequently used                                                                               |

| Scissor Shearing/<br>Guillotine      | Low tooling costs.  Minimal/ no software set-up.  Ease of operation.                                                                 | Severe shock – high risk of mechanical cracks. Potentially high scrap rate.                                                                         | Not generally recommended.                                                                                                     |

| Blanking/ Die<br>Shearing/ Punch-Out | Fast processing times.<br>Virtually any PCB shape.                                                                                   | High tooling costs.  Potential for shock – depending upon supporting fixtures.  Less flexibility – tooling changes required.                        | Usually used for processing high volume of assemblies.                                                                         |

| Circular Rolling<br>Blades           | Low tooling costs.  Minimal/ no software set-up. Ease of operation. Less stress exerted when compared with Shearing.                 | Some machines are operator dependant. For example, operators hold PCB sides – excessive mechanical stress can still be created.                     | Frequently used by customers processing low to moderate volume of assemblies.                                                  |

| Sawing                               | Wedge-shaped knives shear panel with gentle rocking motion along the whole length of the section to be cut – less stress exerted.    | Some machines are operator dependant. For example, operators hold PCB sides – excessive mechanical stress can still be created.                     | Exerts less mechanical stress when compared with manual, guillotine, blanking and circular blades.                             |

| Routing                              | Flexibility. Virtually any PCB shape. Reduces mechanical stress. No/ minimal tooling changes required. Good quality PCB edge finish. | Software set-up. Relatively slow processing times. Initial costs when compared with some of the other depaneling systems.                           | Exerts less mechanical stress when compared with manual, guillotine, blanking and circular blades.                             |

| Laser Cutting                        | Flexibility. Virtually any PCB shape. No mechanical stress. No/ minimal tooling changes required.                                    | Initial costs and maintenance costs.  Depaneled edge often charred and can be jagged.  Extra cleaning process possibly required to remove charring. | Very good regarding no mechanical stress but is costly and not frequently used by customers.                                   |

| Water Jet                            | Flexibility. Virtually any PCB shape. *No mechanical stress. No/ minimal tooling changes required.                                   | Initial costs and maintenance costs. Process can be slow. Noisy operation. Water removal and treatment environmental issues.                        | * There are conflicting reports regarding the level of stress exerted onto the PCB. Also, water jets appear to be rarely used. |

When reviewing depaneling methods it is recommended that customers contact equipment manufacturers to help evaluate what type of system is most suitable based on processing times, flexibility, costs and mechanical stress exerted.

Knowles (UK) Limited, Old Stoke Road, Arminghall, Norwich, Norfolk, NR14 8SQ, United Kingdom

Tel: +44 (0) 1603 723300 Tel. (Sales): 01603 723310 Fax: +44 (0) 1603 723301 Email: <u>SyferSales@knowles.com</u>

Web: www.knowlescapacitors.com/syfer

# Capacitance Ageing of Ceramic Capacitors

Explanation of the natural ageing process resulting in logarithmic loss of Capacitance

| Introduction                                                  | 2 |

|---------------------------------------------------------------|---|

| Law of Capacitance Ageing                                     | 2 |

| Capacitance Measurements                                      | 3 |

| Ageing Allowances                                             | 3 |

| Test Temperature                                              | 4 |

| Test Frequency and Voltage                                    | 5 |

| Measuring Equipment and Measurement Uncertainties             | 5 |

| Resetting the Ageing Process                                  | 6 |

| Capacitance Tolerance & Circuit Application                   | 6 |

| Summary & Conclusions                                         | 6 |

| Appendix 1 Tolerance Correction For Ageing Rates of 1% and 6% | 8 |

Page 2 of 8

#### **Introduction**

Capacitor ageing (Capacitance Drift) is a term used to describe the negative, logarithmic capacitance change that takes place in ceramic capacitors with time. The ageing process has a negligible affect on Class 1 (COG) product but should be taken into account when measuring Class 2 (X7R, Y5V & Z5U) product.

The crystalline structure for Barium Titanate based ceramics changes on passing through its Curie temperature (known as the Curie Point) at approximately 125°C. The domain structure relaxes with time and in doing so, the dielectric constant reduces logarithmically, this is known as the ageing mechanism of the dielectric constant. The more stable dielectrics have the lowest ageing rates.

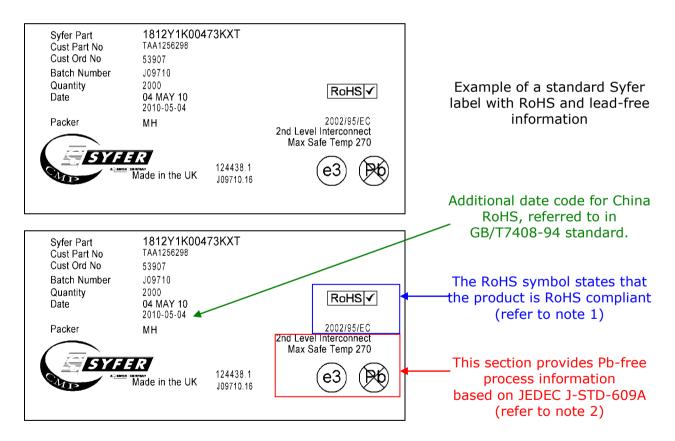

The start point for the ageing process is indicated for all product supplied by Syfer by the date stated on the packaging labels. If the ageing start point is not known then the ageing process can be reset by heating the capacitors to a temperature above the Curie Point. The ageing process then starts again from zero.

#### **Law of Capacitance Ageing**

During the first hour after cooling through the Curie temperature, the loss of capacitance is not well defined, but after this time it follows a logarithmic law that can be expressed in terms of an ageing constant.

The ageing constant 'k', or ageing rate, is defined as the percentage loss of capacitance due to the ageing process of the dielectric that occurs during a decade of time (a tenfold increase in age) and is expressed as percent per logarithmic decade of hours. As the law of decrease of capacitance is logarithmic, this means that in a capacitor with an ageing rate of 1% per decade of time, the capacitance will decrease at a rate of:

- i) 1% between 1 and 10 hours

- ii) an additional 1% between the following 10 and 100 hours

- iii) an additional 1% between the following 100 and 1,000 hours

- iv) an additional 1% between the following 1,000 and 10,000 hours etc.

The ageing rate continues in this manner throughout the capacitors life.

An alternative method of expressing this is that the percentage loss of capacitance will be 2 times k' between 1 and 100 hours and 3 times k' between 1 and 1,000 hours. This may be expressed mathematically by the following equation:

Page 3 of 8

Where: C<sub>t</sub> is the capacitance t hours after the start of the ageing process

$C_1$  is the capacitance 1 hour after the start of the ageing process

k is the ageing constant in percent per decade (as defined above)

t is the time in hours from the start of the ageing process

The ageing constant may be declared by the manufacturer for a particular ceramic dielectric, or it may be determined by de-ageing the capacitor and measuring the capacitance at two known times thereafter.

Typical values of the ageing constant for Syfer Technology ceramic capacitors are:

| Dielectric Class | Typical Value      |  |  |

|------------------|--------------------|--|--|

| C0G (CG/1B)      | Negligible         |  |  |

| X7R (2C1)        | 1 to 2% per decade |  |  |

Example of a different dielectric material/ type offered by other capacitor manufacturers:

Dielectric Class

Z5U (2F4)

Typical Value

6% per decade

#### **Capacitance Measurements**

Ageing Allowances

Because of ageing, it is necessary to specify an age for reference measurements at which the capacitance shall be within the prescribed tolerance. This is fixed at 1,000 hours, since for practical purposes there is not much further loss of capacitance after this time.

In order to calculate the capacitance  $C_{1000}$  after 1,000 hours the following formula may be used:

$$C_{1000} = C_t \begin{bmatrix} 1 - \frac{k}{100} & (3 - \log_{10}t) \end{bmatrix}$$

Page 4 of 8

For measurements during the course of capacitor manufacture, the loss of capacitance from the time of measurement to the 1,000 hour age will be known and can be off-set by using asymmetric inspection tolerances. For example, if it is known that the total capacitance loss to 1,000 hours will be 5%, then the capacitors may be inspected to limits of say -15%/+25% instead of  $\pm$  20%.

All capacitors shipped are within their specified tolerance at the standard reference age of 1,000 hours after cooling through their Curie temperature.

Ageing begins after cooling from above the Curie point and continues, apparently forever. This capacitance loss does not limit the effective life of the capacitor, however, it should not be overlooked. A 1% change of capacitance value between 1 and 10 hours may seem serious but 1% change between 10,000 and 100,000 hours is less significant.

Refer to Appendix 1 showing the tolerance correction (for standard reference age of 1,000 hours) to allow for ageing rates of 1% and 6% between 12 and 10,000 hours.

#### **Ageing Allowance Example**

A capacitor with a tolerance of  $\pm$  20% is measured after 3750 hours from its last heat cycle. The corrected tolerance limits to which it should be tested are:

a) For 1% ageing; tolerance correction is: -0.6%

Therefore, tolerance range allowed is: -20.6% to +19.4%

b) For 6% ageing; tolerance correction is: -3.4%

Therefore, tolerance range allowed is: -23.4% to +16.6%

#### Test Temperature

Capacitance is normally declared at a reference temperature, this varies according to specification dependent on country of origin, for example CECC specifies  $20^{\circ}\text{C} \pm 2^{\circ}\text{C}$ .

Capacitors measured at Syfer are tested in accordance with CECC specifications at 20°C. If capacitors are tested at a different temperature then allowances should be made when verifying the capacitance value.

Care should be taken when testing capacitors. Errors can arise if capacitors are heated by body heat through handling and it is recommended that for precision measurement plastic tweezers be used to handle capacitors.

Page 5 of 8

#### Test Frequency and Voltage

The following table details the frequency and voltage settings used for electrical testing of surface mount and radial product types by dielectric classification.

| Dielectric  | Surface                    | e Mount                    | Radial product    |                    |  |

|-------------|----------------------------|----------------------------|-------------------|--------------------|--|

| Class       | Test<br>Frequency          | Test Voltage<br>(rms)      | Test<br>Frequency | Test Voltage (rms) |  |

| C0G (CG/1B) | ≥1nF = 1kHz<br><1nF = 1MHz | 1.0V                       | 1kHz              | 1.0V               |  |

| X7R (2C1)   | 1kHz                       | >25V = 1.0V<br>≤25V = 0.5V | 1kHz              | 0.5V               |  |

#### Measuring Equipment and Measurement Uncertainties

Incorrect capacitance measurement can also be introduced as a result of either the accuracy of the equipment and/ or measurement uncertainties.

- Measuring equipment. The accuracy and precision of the measuring device/ meter should be examined to determine if the meter is capable of measuring the capacitor adequately.

- Measurement uncertainties. Errors should be removed before measuring the capacitors. For example, by performing open and short-circuit compensations.

- Low capacitance measurements can be affected by stray capacitance from equipment test leads. It is recommended that when measuring values less than 50pF test fixtures are used to minimise the possibility of stray capacitance.

- As a result of the piezoelectric nature of ceramic capacitors, tweezer pressure can also affect capacitance measurements.

- Low capacitance radial products can also be affected by stray capacitance from the components legs/ leads. It is recommended that radial products are measured across the leads directly next to the component body.

Page 6 of 8

#### **Resetting the Ageing Process**

For Class 1 (COG) ceramics the ageing rate is negligible. For Class 2 ceramics it may be necessary to reset the ageing process.

The ageing process is reset by heating the dielectric above its Curie Point. To ensure that all capacitors have been sufficiently heated and that the ageing process has been reset it recommended that capacitors are placed in an oven @  $160^{\circ}$ C for  $1\frac{1}{2}$  hours separated on a metal tray. After the heating process, the capacitors should then be allowed to stabilise at room temperature ( $20^{\circ}$ C  $\pm$   $2^{\circ}$ C) for 24 hours before capacitance measurements are conducted.

#### **<u>Capacitance Tolerance & Circuit Application</u>**

Capacitance ageing is inherent in class 2 ceramic capacitors and it is important for circuit designs to recognise and allow for this effect. It is of particular importance when initial capacitance tolerance must be tight. In these circumstances the ageing rate may cause the capacitors to drift out of tolerance on the low side. For example, it would be imprudent to specify a 5% tolerance for a unit with a 2% ageing rate.

Designing the capacitor with an initial value large enough to compensate for long term ageing will cause the units to be out of tolerance on the high side each time de-ageing occurs. This can be especially true for equipment where an ambient operating temperature of  $+125^{\circ}$ C could cause potential de-ageing. For this reason tight tolerance capacitors should be of class 1 dielectric when possible.

#### **Summary & Conclusions**

- 1. Electrical Tests. The recommended sequence for testing Multilayer Ceramic Capacitors is:

- i) Insulation Resistance (IR)

- ii) Voltage Proof (VP)/ Dielectric Withstand Voltage (DWV)

- iii) De-age Class 2 capacitors and allow to stabilise at room temperature for 24 hours before capacitance measurements are conducted.

- iv) Capacitance, apply factors based on the manufacturers ageing rate and the time elapsed since the last Curie temperature excursion.

- v) Dissipation Factor.

- vi) Other Tests. If any limits are specified for change in capacitance during a long term test, the capacitor should be de-aged before both the initial and final measurements.

- 2. With surface mount MLC's some of the solder termination materials used will diffusion bond at temperatures close to that of the ceramic Curie temperature. It is, therefore, important that when de-ageing these products they should be placed on a tray such that their termination end surfaces are not in contact with each other.

- 3. The ageing process is completely repeatable and predictable for a given capacitor.

- 4. Capacitance change is negative and logarithmic in respect to time.

- 5. Application of a D.C. bias can move the point on the ageing curve forward in time. When a D.C. voltage is applied at elevated temperatures (below the Curie Point) the capacitor will show a loss of capacitance but with a consequently lower ageing rate.

- 6. Class 1 CG/1B (COG) dielectric has a negligible ageing rate.